## SEEE 1223 DIGITAL ELECTRONICS CHAPTER 6: COMBINATIONAL MSI

#### DR. MOHD SAIFUL AZIMI BIN MAHMUD

P19a-04-03-30 School of Electrical Engineering Faculty of Engineering Universiti Teknologi Malaysia 019-7112948 azimi@utm.my

0101100 1001010 1001010

# **MSI CIRCUIT**

## **MSI CIRCUIT** INTRODUCTION

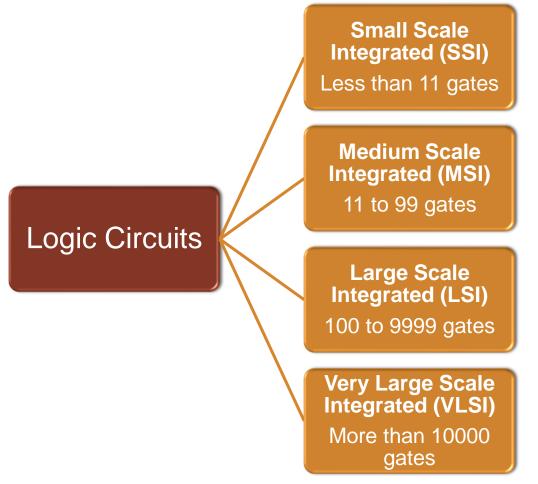

MSI (Medium scale integrated) circuits are logic circuit that contains 11 to 99 logic gates in a circuit.

#### innovative • entrepreneurial • global

## **MSI CIRCUIT INTRODUCTION**

D0

D1

D2

D3

74x47

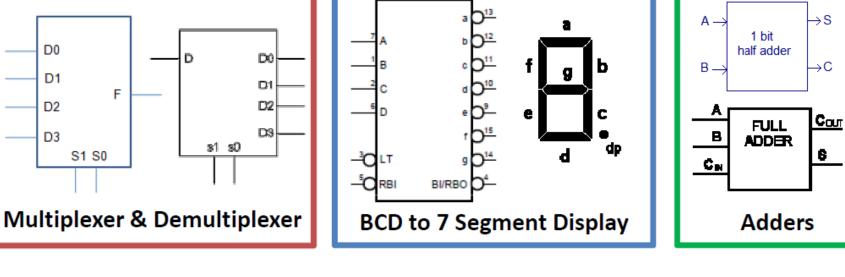

# MULTIPLEXER

## **MULTIPLEXER** INTRODUCTION

- Multiplexer (Mux) is a device that allows digital information from several sources to be routed onto a single line for transmission over that line to a common destination.

- Basic Multiplexer has 2<sup>n</sup> data-inputs, n data-selector inputs and one single output.

- Multiplexers are also known as data selectors.

- Multiplexers usually written as  $(Y) \times 1$  or (Y): 1, where Y is the number of input data lines.

#### Example

A 4 input data line multiplexer is written as 4:1 mux.

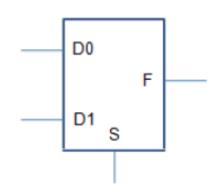

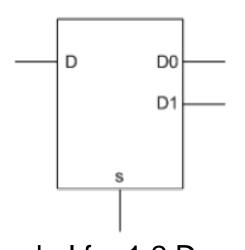

#### **MULTIPLEXER** 2:1 MUX

- 2:1 Mux consists of 2 inputs, 1 selector and 1 output.

Function: F = D0 when S = 0F = D1 when S = 1

#### Function Table

| S | F          |

|---|------------|

| 0 | <i>D</i> 0 |

| 1 | D1         |

Symbol for 2:1 Mux

- How to design a 2:1 mux using:

- K-map? What are the input and output?

- By inspection of its function?

## **MULTIPLEXER** 2:1 MUX

- Design **2:1 Mux** using K-map.

- As we known, 2:1 mux consists of 2 inputs, 1 output and 1 selector.

- Inputs = **D0**, **D1**, **S**

N

• Output = F

| Functior | 1:                    |

|----------|-----------------------|

| F = D0   | when <mark>S</mark> = |

F = D1 when S = 1

**Truth Table**

$D1 \begin{array}{c} D0, S \\ 00 & 01 & 11 & 10 \\ 0 & 0 & 0 & 1 \\ 1 & 0 & 1 & 1 \\ 0 & 1 & 1 & 1 \\ D1 \cdot S \end{array} D0 \cdot \overline{S}$

$F = D0 \cdot \bar{S} + D1 \cdot S$

Can you draw the logic circuit?

## **MULTIPLEXER** 2:1 MUX

• Design **2:1 Mux** by inspection of its function

As we know, 2:1 mux function:

$$F = D0$$

when  $S = 0$   $\longrightarrow$   $F = D0 \cdot \overline{S}$

$F = D1$  when  $S = 1$   $\longrightarrow$   $F = D1 \cdot S$

Symbol for 2:1 Mux

• Therefore,  $F = D0 \cdot \overline{S} + D1 \cdot S$

K-map? What are the input and output?

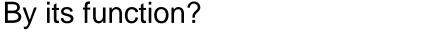

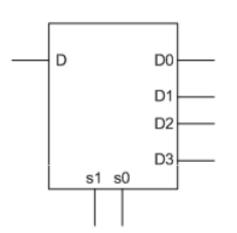

## **MULTIPLEXER** 4:1 MUX

Symbol for 4:1 Mux

ullet

How to design a 4:1 mux using:

• 4:1 Mux consists of 4 inputs, 2 selectors and 1 output.

#### **Function Table**

| <i>S</i> 1 | <i>S</i> 0 | F          |

|------------|------------|------------|

| 0          | 0          | <i>D</i> 0 |

| 0          | 1          | D1         |

| 1          | 0          | D2         |

| 1          | 1          | D3         |

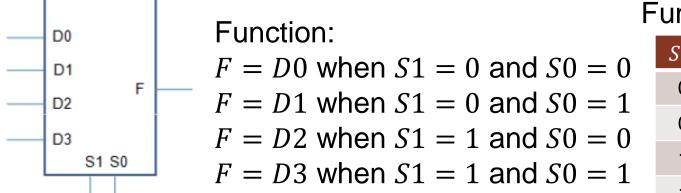

## **MULTIPLEXER** 4:1 MUX

- Since 4:1 Mux has six inputs (*D*3, *D*2, *D*1, *D*0, *S*1, *S*0) and one output (*F*), therefore it is difficult/time consuming to use K-maps.

- Thus by looking at the functions of 4:1 mux:

Symbol for 4:1 Mux

• Therefore,  $F = D0 \cdot \overline{S1} \cdot \overline{S0} + D1 \cdot \overline{S1} \cdot S0 + D2 \cdot S1 \cdot \overline{S0} + D3 \cdot S1 \cdot S0$

Can you draw the logic circuit?

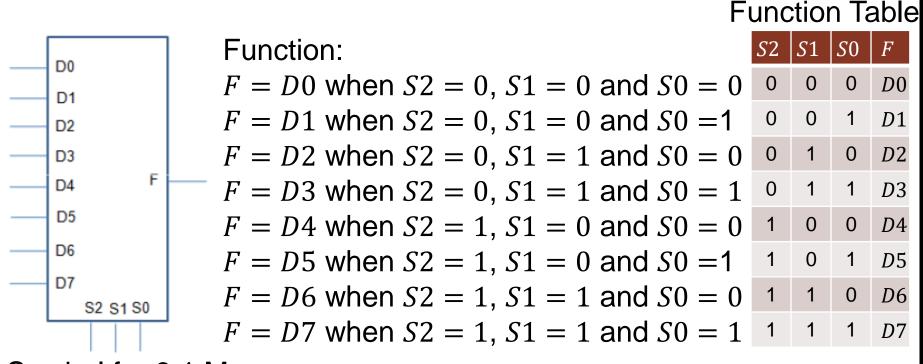

#### **MULTIPLEXER** 8:1 MUX

• 8:1 Mux consists of 8 inputs, 3 selectors and 1 output.

Symbol for 8:1 Mux

What is the logic expression for *F*?

#### **MULTIPLEXER** MULTIPLEXER APPLICATIONS

#### Example

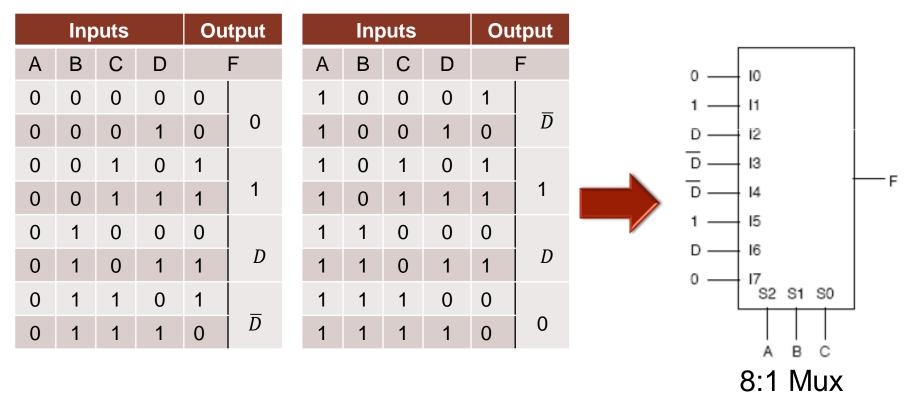

Implement  $F(A, B, C, D) = \sum m(2, 3, 5, 6, 8, 10, 11, 13)$  using an 8:1 Mux

## **MULTIPLEXER** MULTIPLEXER EXPANSIONS

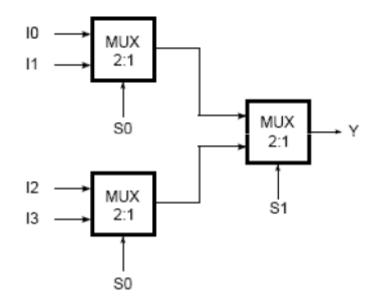

• A few multiplexers can be combined to built a bigger multiplexer.

## Example

A 4:1 Mux can be built by combining three 2:1 Mux.

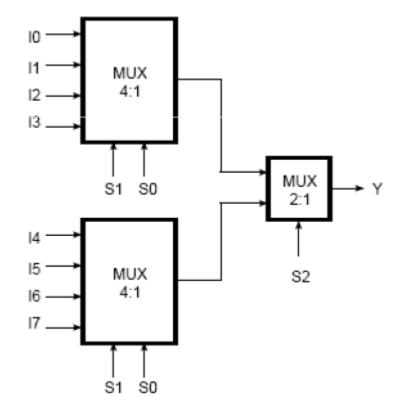

#### **MULTIPLEXER** MULTIPLEXER EXPANSIONS

A 8:1 Mux can be built by combining **two** 4:1 Mux and **one** 2:1 Mux.

## **MULTIPLEXER** MULTIPLEXER INTEGRATED CIRCUIT (IC)

- Mux (and other common logic blocks) can be bought as a packaged integrated circuits (IC).

- Commonly used IC is TTL (Transistor-Transistor Logic) and CMOS (Complementary Metal-Oxide Semiconductor).

#### Example

An inverter IC in TTL is named 74LS04 (LS for Low Speed TTL). While inverter IC in CMOS is named 74HC04 (HC for High Speed CMOS).

- 2:1 Mux IC: 74LS157/74HC157 (74x157)

- 4:1 Mux IC: 74LS153/74HC153 (74x153)

- 8:1 Mux IC: 74LS151/74HC151 (74x151)

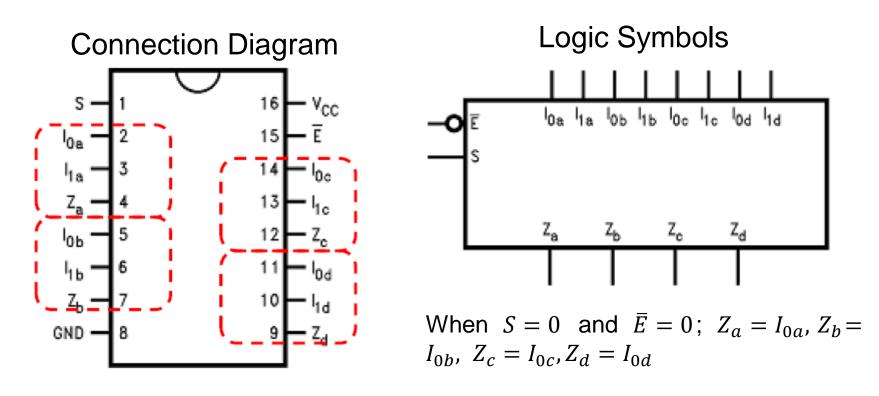

## **MULTIPLEXER** MULTIPLEXER IC: 74x157 (QUAD 2:1 MUX)

- 74x157 is a quad 2:1 Mux.

- Contains of four 2:1 Mux.

- Controlled by a single common selector input.

- It has one active-low enable input.

## **MULTIPLEXER** MULTIPLEXER IC: 74x157 (QUAD 2:1 MUX)

#### **Truth Table**

|                | In | Output         |       |   |

|----------------|----|----------------|-------|---|

| $\overline{E}$ | S  | I <sub>0</sub> | $I_1$ | Ζ |

| Н              | Х  | Х              | Х     | L |

| L              | Н  | Х              | L     | L |

| L              | Н  | Х              | Н     | Н |

| L              | L  | L              | Х     | L |

| L              | L  | Н              | Х     | Н |

H = HIGH Voltage Level

L= LOW Voltage Level

X = Immaterial (Irrelevant)

Output *Z* selects  $I_0$  or  $I_1$  depending on select *S* (with E = 0)

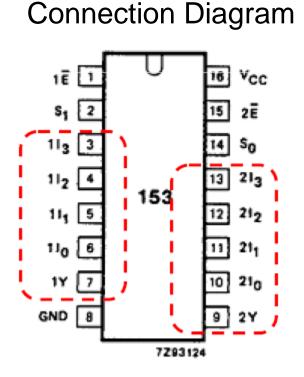

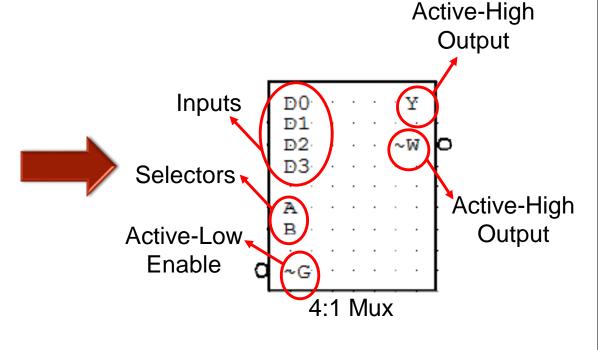

## **MULTIPLEXER** MULTIPLEXER IC: 74x153 (DUAL 4:1 MUX)

- 74x153 is a dual 4:1 Mux.

- Contains of two 4:1 Mux.

- Controlled by a two common selector input.

- It has two **active-low** enable input.

Logic Symbols

UTIVERSITI TEKNOLOGI MALAYS

#### **Function Table**

| SELECT         |                |                 | DATA INPUTS     |                 |                 | OUTPUT<br>ENABLE | OUTPUT |

|----------------|----------------|-----------------|-----------------|-----------------|-----------------|------------------|--------|

| S <sub>0</sub> | S <sub>1</sub> | nl <sub>0</sub> | nl <sub>1</sub> | nl <sub>2</sub> | nl <sub>3</sub> | nĒ               | nY     |

| Х              | Х              | Х               | Х               | Х               | Х               | Н                | L      |

| L              | L              | L               | х               | Х               | Х               | L                | L      |

| L              | L              | н               | X               | х               | X               | L                | н      |

| н              | L              | Х               | L               | х               | Х               | L                | L      |

| н              | L              | Х               | н               | Х               | Х               | L                | н      |

| L              | н              | х               | x               | L               | X               | L                | L      |

| L              | н              | Х               | X               | н               | Х               | L                | н      |

| н              | н              | х               | X               | х               | L               | L                | L      |

| Н              | н              | Х               | Х               | Х               | н               | L                | н      |

Output nY selects  $nl_0$ ,  $nl_1$ ,  $nl_2$  or  $nl_3$  depending on  $S_1$  and  $S_0$  (with  $n\overline{E} = 0$ ).

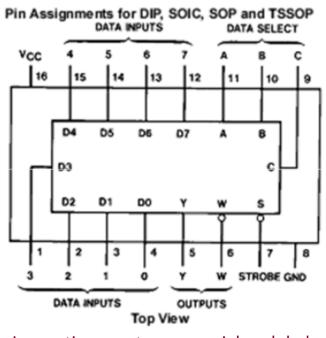

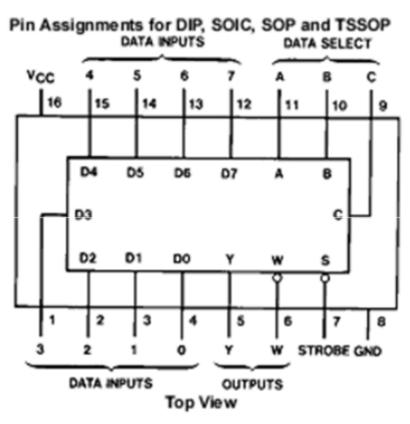

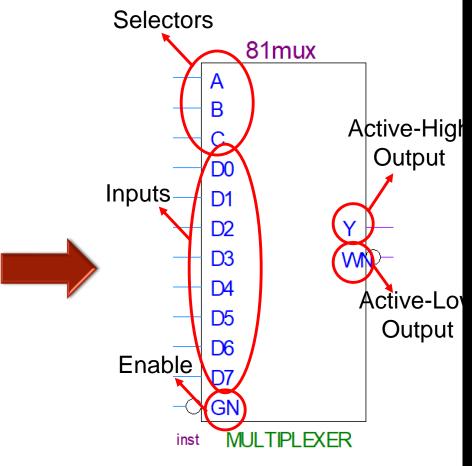

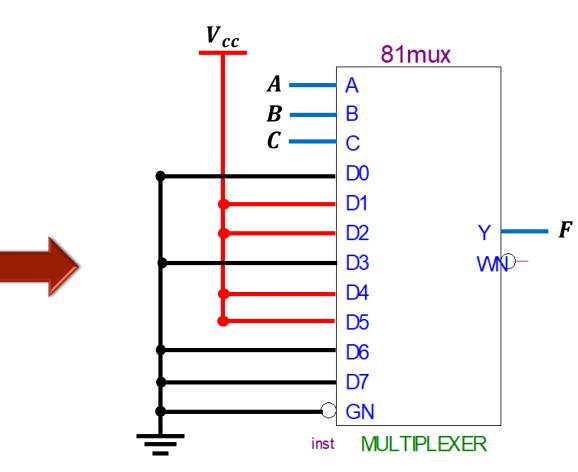

## **MULTIPLEXER** MULTIPLEXER IC: 74x151 (8:1 MUX)

- 74x151 is a 8:1 Mux.

- Contains of one 8:1 Mux.

- It has two outputs

- 1. Active High

- 2. Active Low

- It has one active-low enable input.

#### **MULTIPLEXER** MULTIPLEXER IC: 74x151 (8:1 MUX)

#### **Connection Diagram**

#### **Truth Table**

|   | Ir    | Outp | outs   |    |                 |

|---|-------|------|--------|----|-----------------|

|   | Selec | t    | Strobe |    |                 |

| С | В     | А    | S      | Y  | W               |

| Х | Х     | Х    | Н      | L  | Н               |

| L | L     | L    | L      | D0 | $\overline{D0}$ |

| L | L     | Н    | L      | D1 | $\overline{D1}$ |

| L | Н     | L    | L      | D2 | $\overline{D2}$ |

| L | Н     | Н    | L      | D3 | $\overline{D3}$ |

| н | L     | L    | L      | D4 | $\overline{D4}$ |

| н | L     | Н    | L      | D5 | $\overline{D5}$ |

| н | Н     | L    | L      | D6 | D6              |

| Н | Н     | Н    | L      | D7 | $\overline{D7}$ |

## MULTIPLEXER REVIEWS

- How to design a 3:1 Mux or a 7:1 Mux?

- 3:1 Mux is structured as 4:1 Mux

- 7:1 Mux is structured as 8:1 Mux

- How many select bits is needed for 16:1 Mux?

- 4 select inputs (S3, S2, S1, S0)

- How many inputs does a 32:1 Mux have?

- 5 select bits and 32 input data lines (37 inputs)

# DEMULTIPLEXER

## **DEMULTIPLEXER** INTRODUCTION

- Demultiplexer (Demux) perform in the inverse of the mux function.

- It takes data from one line and distribute to given number and of output lines.

- Basic Demultiplexer has one input, n data-selector inputs and 2<sup>n</sup> output.

- Demultiplexer usually written as 1x(Y) or 1:(Y), where Y is the number of output data lines.

#### Example

A 4 output data line demultiplexer is written as 1:4 demux.

## **DEMULTIPLEXER** 1:2 DEMUX

• 1:2 Demux consists of 1 input, 1 selector and 2 outputs.

Symbol for 1:2 Demux

**Function:** D0 = D, D1 = 0 when  $S = 0 \longrightarrow D0 = D \cdot \overline{S}$ D0 = 0, D1 = D when  $S = 1 \longrightarrow D1 = D \cdot S$ **Function Table D**1 **D**0 S 0 0 D Logic circuit 1 D 0 D0 D1

## **DEMULTIPLEXER** 1:4 DEMUX

• 1:4 Demux consists of 1 input, 2 selectors and 4 outputs.

Symbol for 1:4 Demux

Function:

$$D0 = D \text{ when } S1 = 0 \text{ and } S0 = 0 \longrightarrow D0 = D \cdot \overline{S1} \cdot \overline{S0}$$

$$D1 = D \text{ when } S1 = 0 \text{ and } S0 = 1 \longrightarrow D1 = D \cdot \overline{S1} \cdot S0$$

$$D2 = D \text{ when } S1 = 1 \text{ and } S0 = 0 \longrightarrow D2 = D \cdot S1 \cdot \overline{S0}$$

$$D3 = D \text{ when } S1 = 1 \text{ and } S0 = 1 \longrightarrow D3 = D \cdot S1 \cdot S0$$

#### **Function Table**

*S*1 *S*0 *D*3 D2 *D*1 D00 D 0 0 0 0 0 1 0 0 D 0 1 0 0 D 0 0 1 1 D 0 0 0

## DECODER

## **DECODER** INTRODUCTION

- **Decoder** used to detect the presence of specified combination of bits (code) on its inputs and indicates the presence of that code by a specific output level.

- It has *n* inputs and  $2^n$  outputs (*n*-to- $2^n$ ).

- Decoder can be designed as 1-to-2, 2-to-4, 3-to-8, 4-to-16 and etc.

- If **enable inputs** is presents, it must be asserted to enable decoder function.

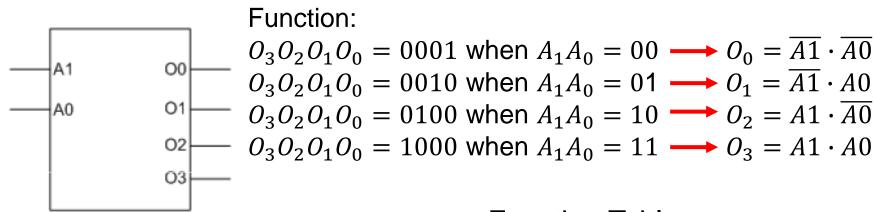

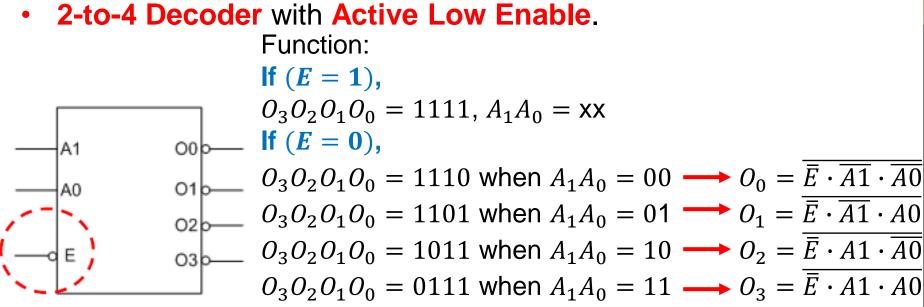

#### **DECODER** 2-to-4 DECODER

2-to-4 Decoder consists of 2 inputs and 4 outputs.

Symbol for Active High 2-to-4 Decoder

#### **Function Table**

| Inp        | uts        |                       | Outputs |    |                       |  |

|------------|------------|-----------------------|---------|----|-----------------------|--|

| <i>A</i> 1 | <i>A</i> 0 | <i>0</i> <sub>3</sub> | 02      | 01 | <i>O</i> <sub>0</sub> |  |

| 0          | 0          | 0                     | 0       | 0  | 1                     |  |

| 0          | 1          | 0                     | 0       | 1  | 0                     |  |

| 1          | 0          | 0                     | 1       | 0  | 0                     |  |

| 1          | 1          | 1                     | 0       | 0  | 0                     |  |

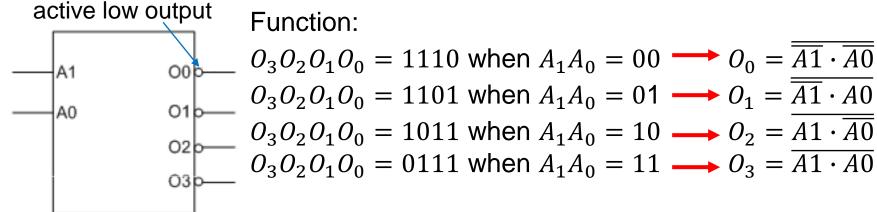

## **DECODER** 2-to-4 DECODER

• Typically, decoders are designed as Active Low.

Bubble at output denotes

Symbol for Active Low 2-to-4 Decoder

#### **Function Table**

| Inp        | Inputs     |                       | Outputs |    |                       |

|------------|------------|-----------------------|---------|----|-----------------------|

| <i>A</i> 1 | <i>A</i> 0 | <i>0</i> <sub>3</sub> | 02      | 01 | <i>O</i> <sub>0</sub> |

| 0          | 0          | 1                     | 1       | 1  | 0                     |

| 0          | 1          | 1                     | 1       | 0  | 1                     |

| 1          | 0          | 1                     | 0       | 1  | 1                     |

| 1          | 1          | 0                     | 1       | 1  | 1                     |

## **DECODER** 2-to-4 DECODER

Symbol for Active Low 2-to-4 Decoder with Active Low Enable

|         | Е   | Inp        | uts        | Outputs               |    |    |    |  |

|---------|-----|------------|------------|-----------------------|----|----|----|--|

| able    |     | <i>A</i> 1 | <i>A</i> 0 | <i>0</i> <sub>3</sub> | 02 | 01 | 00 |  |

| Ца      | 1   | Х          | Х          | 1                     | 1  | 1  | 1  |  |

| uo      | 0   | 0          | 0          | 1                     | 1  | 1  | 0  |  |

| unction | 0   | 0          | 1          | 1                     | 1  | 0  | 1  |  |

| n       | 0   | 1          | 0          | 1                     | 0  | 1  | 1  |  |

| ш.      | 0   | 1          | 1          | 0                     | 1  | 1  | 1  |  |

|         | hal |            |            |                       |    |    | 00 |  |

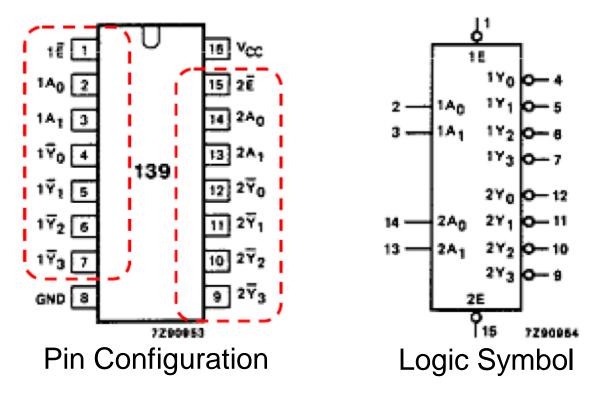

## **DECODER** DECODER IC: 74x139 (2-to-4 DECODER)

- 74x139 contains two 2-to-4 Decoders.

- To use either decoder, it must be enabled by inputting low signal at the enable input.

- When enable = High, all output = High.

#### **Function Table**

| Inputs |                 |        | Outputs           |                   |                   |                   |  |

|--------|-----------------|--------|-------------------|-------------------|-------------------|-------------------|--|

| nĒ     | nA <sub>0</sub> | $nA_1$ | $n\overline{Y_0}$ | $n\overline{Y_1}$ | $n\overline{Y}_2$ | $n\overline{Y_3}$ |  |

| Н      | Х               | Х      | Н                 | Н                 | Н                 | Н                 |  |

| L      | L               | L      | L                 | Н                 | Н                 | Н                 |  |

| L      | Н               | L      | Н                 | L                 | Н                 | Н                 |  |

| L      | L               | Н      | Н                 | Н                 | L                 | Н                 |  |

| L      | Н               | Н      | Н                 | Н                 | Н                 | L                 |  |

H = HIGH Voltage Level

L= LOW Voltage Level

X = Don't care

#### Outputs depends on inputs A with E = 0

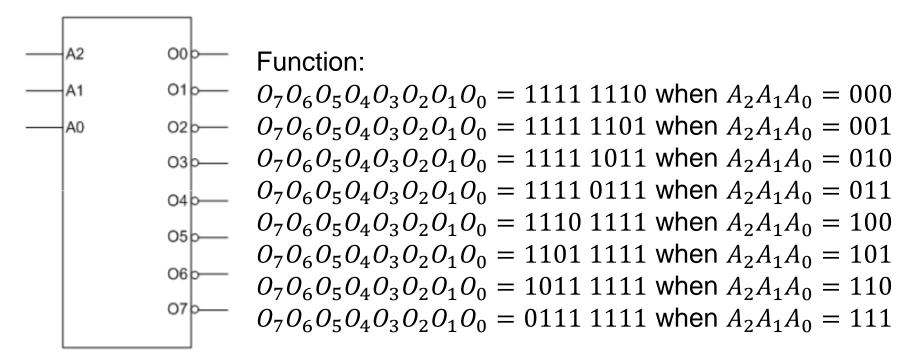

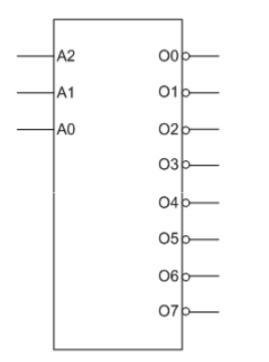

## **DECODER** 3-to-8 DECODER

• 3-to-8 Decoder consists of 3 inputs and 8 outputs.

Symbol for Active Low 3-to-8 Decoder

### **DECODER** 3-to-8 DECODER

#### 3-to-8 Decoder consists of 3 inputs and 8 outputs.

Symbol for Active Low 3-to-8 Decoder **Function Table**

| I  | Inputs |    |    | Outputs |    |    |    |    |    |    |

|----|--------|----|----|---------|----|----|----|----|----|----|

| A2 | A1     | A0 | 07 | 06      | O5 | O4 | O3 | O2 | 01 | 00 |

| 0  | 0      | 0  | 1  | 1       | 1  | 1  | 1  | 1  | 1  | 0  |

| 0  | 0      | 1  | 1  | 1       | 1  | 1  | 1  | 1  | 0  | 1  |

| 0  | 1      | 0  | 1  | 1       | 1  | 1  | 1  | 0  | 1  | 1  |

| 0  | 1      | 1  | 1  | 1       | 1  | 1  | 0  | 1  | 1  | 1  |

| 1  | 0      | 0  | 1  | 1       | 1  | 0  | 1  | 1  | 1  | 1  |

| 1  | 0      | 1  | 1  | 1       | 0  | 1  | 1  | 1  | 1  | 1  |

| 1  | 1      | 0  | 1  | 0       | 1  | 1  | 1  | 1  | 1  | 1  |

| 1  | 1      | 1  | 0  | 1       | 1  | 1  | 1  | 1  | 1  | 1  |

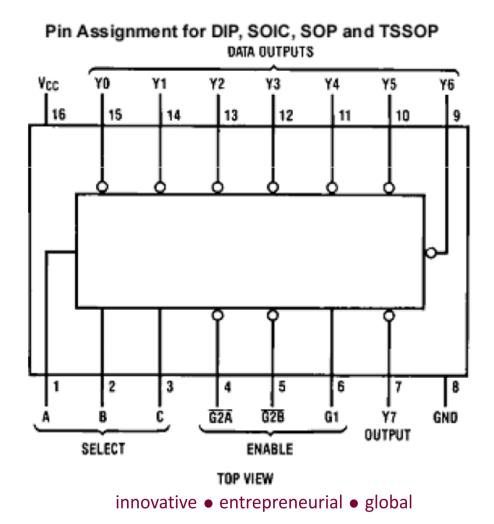

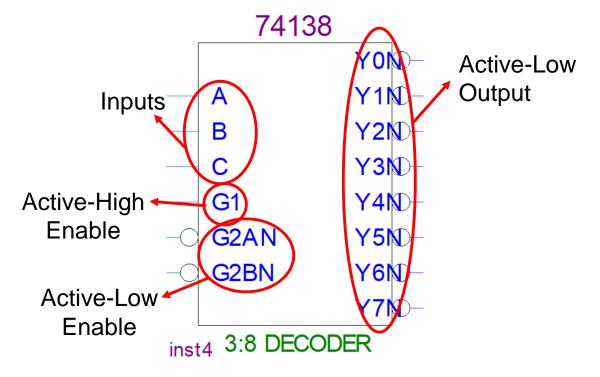

## **DECODER** DECODER IC: 74x138 (3-to-8 DECODER)

- 74x138 contains one 3-to-8 Decoder. (a popular device)

- It has 3 inputs, 3 enables and 8 outputs.

## **DECODER** DECODER IC: 74x138 (3-to-8 DECODER)

UTTM UNIVERSITI TEKNOLOGI MALAYSIA

**Function Table**

|            | Inputs          |   |        |   | Outputs |    |    |    |    |    |    |    |

|------------|-----------------|---|--------|---|---------|----|----|----|----|----|----|----|

| Ena        | able            |   | Select |   |         |    |    |    |    |    |    |    |

| <i>G</i> 1 | $\overline{G2}$ | С | В      | А | Y0      | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

| Х          | Н               | Х | Х      | Х | Н       | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| L          | Х               | Х | Х      | Х | Н       | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| Н          | L               | L | L      | L | L       | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| Н          | L               | L | L      | Н | Н       | L  | Н  | Н  | Н  | Н  | Н  | Н  |

| Н          | L               | L | Н      | L | Н       | Н  | L  | Н  | Н  | Н  | Н  | Н  |

| Н          | L               | L | Н      | Н | Н       | Н  | Н  | L  | Н  | Н  | Н  | Н  |

| Н          | L               | Н | L      | L | Н       | Н  | Н  | Н  | L  | Н  | Н  | Н  |

| Н          | L               | Н | L      | Н | Н       | н  | Н  | Н  | Н  | L  | Н  | Н  |

| Н          | L               | Н | Н      | L | Н       | Н  | Н  | Н  | Н  | Н  | L  | Н  |

| Н          | L               | Н | Н      | Н | Н       | Н  | Н  | Н  | Н  | Н  | Н  | L  |

H = HIGH Voltage Level, L= LOW Voltage Level, X = Don't care  $\overline{G2} = \overline{G2A} + \overline{G2B}$

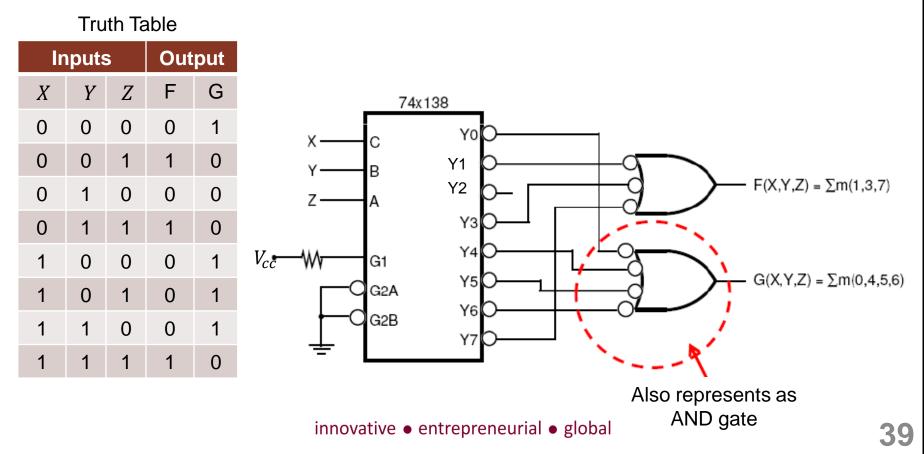

### **DECODER** DECODER APPLICATIONS

### Example

Show how the 3-to-8 Decoder and basic gate can implement the logic function  $F(X, Y, Z) = \sum m(1, 3, 7)$  and  $G(X, Y, Z) = \sum m(0, 4, 5, 6)$

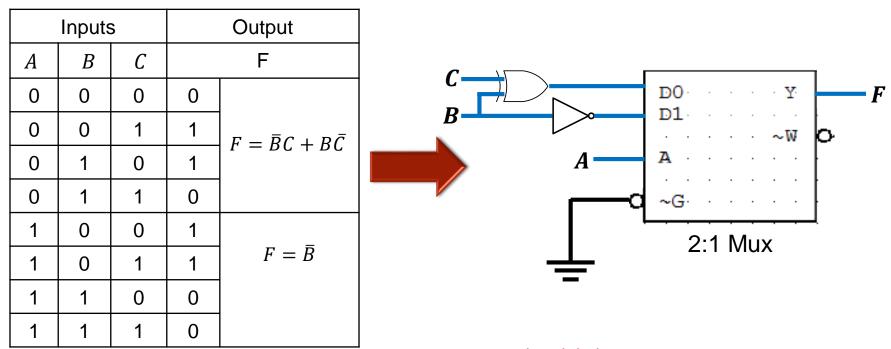

Given  $F(A, B, C) = \sum m(1, 2, 4, 5)$ . Implement using;

- a) 8:1 Mux

- b) 4:1 Mux

- c) 2:1 Mux

- d) 3-to-8 Active Low Decoder

Solution

Using 8:1 Mux

$$F(A, B, C) = \sum m(1, 2, 4, 5)$$

#### **Truth Table**

|   | Inpute | Output |   |

|---|--------|--------|---|

| A | В      | С      | F |

| 0 | 0      | 0      |   |

| 0 | 0      | 1      |   |

| 0 | 1      | 0      |   |

| 0 | 1      | 1      |   |

| 1 | 0      | 0      |   |

| 1 | 0      | 1      |   |

| 1 | 1      | 0      |   |

| 1 | 1      | 1      |   |

Solution

Using 8:1 Mux

$$F(A, B, C) = \sum m(1, 2, 4, 5)$$

#### **Truth Table**

|   | Inpute | Output |   |

|---|--------|--------|---|

| A | В      | С      | F |

| 0 | 0      | 0      | 0 |

| 0 | 0      | 1      | 1 |

| 0 | 1      | 0      | 1 |

| 0 | 1      | 1      | 0 |

| 1 | 0      | 0      | 1 |

| 1 | 0      | 1      | 1 |

| 1 | 1      | 0      | 0 |

| 1 | 1      | 1      | 0 |

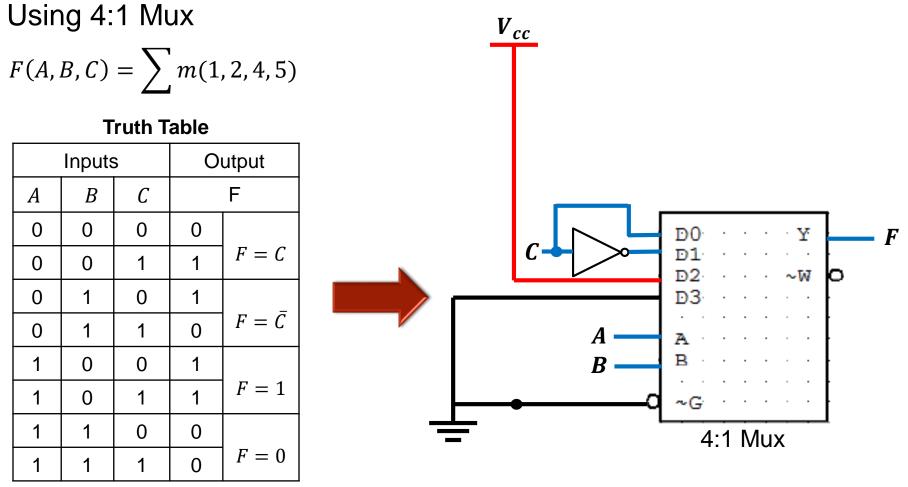

Solution

Using 4:1 Mux

$$F(A, B, C) = \sum m(1, 2, 4, 5)$$

#### **Truth Table**

|   | Inputs | Output |   |                    |  |  |

|---|--------|--------|---|--------------------|--|--|

| A | В      | С      |   | F                  |  |  |

| 0 | 0      | 0      | 0 |                    |  |  |

| 0 | 0      | 1      | 1 | F = C              |  |  |

| 0 | 1      | 0      | 1 | _                  |  |  |

| 0 | 1      | 1      | 0 | $F = \overline{C}$ |  |  |

| 1 | 0      | 0      | 1 |                    |  |  |

| 1 | 0      | 1      | 1 | F = 1              |  |  |

| 1 | 1      | 0      | 0 |                    |  |  |

| 1 | 1      | 1      | 0 | F = 0              |  |  |

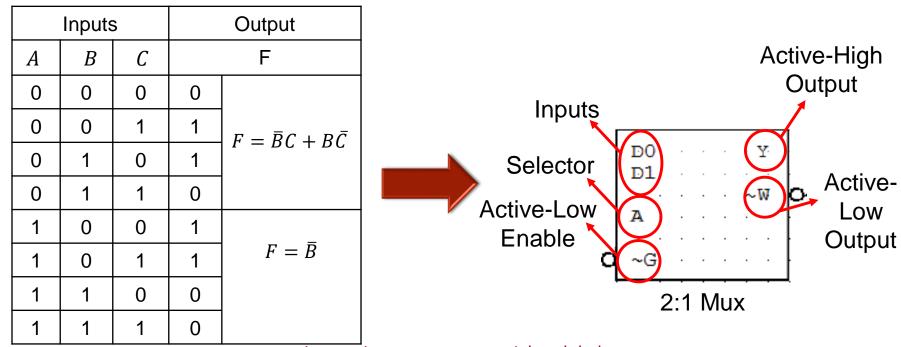

Solution

Using 2:1 Mux

Solution

$$F(A, B, C) = \sum m(1, 2, 4, 5)$$

#### **Truth Table**

Solution

Using 2:1 Mux

$$F(A, B, C) = \sum m(1, 2, 4, 5)$$

#### **Truth Table**

Solution

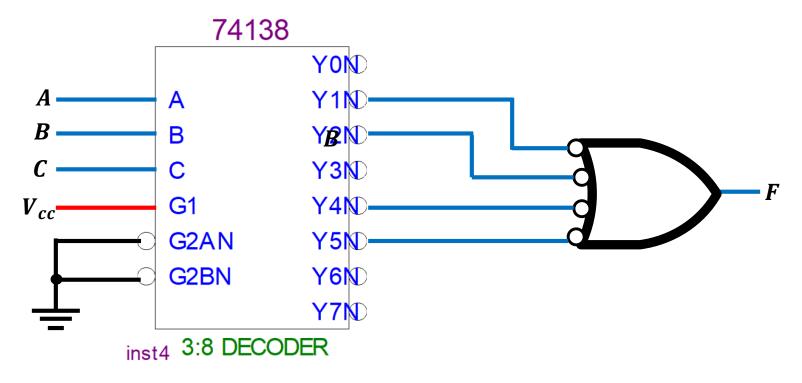

Using 3-to-8 Decoder

$$F(A, B, C) = \sum m(1, 2, 4, 5)$$

Solution

Using 3-to-8 Decoder

$$F(A, B, C) = \sum m(1, 2, 4, 5)$$

# **BOOLEAN FUNCTION USING MULTIPLEXER & DECODER** ASSESSMENT 1

Given Boolean expression  $A \cdot \overline{C} + \overline{A} \cdot \overline{B} \cdot \overline{C} + \overline{A} \cdot \overline{B} \cdot \overline{C} + \overline{A} \cdot (B \oplus C)$ , implement using;

- a) 8:1 Mux

- b) 4:1 Mux

- c) 2:1 Mux

- d) 3-to-8 Active Low Decoder

# **BOOLEAN FUNCTION USING MULTIPLEXER & DECODER** ASSESSMENT 2

Given Boolean expression  $f(X, Y, Z) = \prod (M_0, M_1, M_2, M_4)$ , implement using;

- a) 4:1 Mux

- b) 2:1 Mux

- c) 3-to-8 Active Low Decoder

- d) 2-to-4 Active Low Decoder

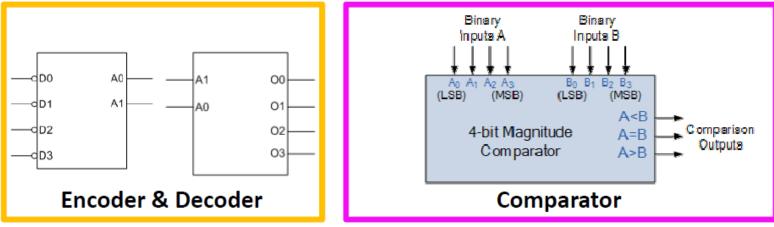

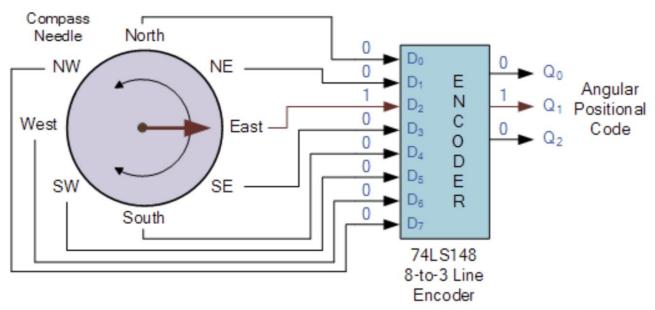

# ENCODER

# **ENCODER** INTRODUCTION

- Encoder performs reverse function of decoder.

- Encoder used to compress the input into a code that contains the same information in fewer bits.

- It has  $2^n$  inputs and n output.  $(2^n to n)$ .

- Only **one input** is allowed to be active at any one time.

Encoder function for Compass (https://www.electronics-tutorials.ws/combination/comb\_4.html)

innovative  $\bullet$  entrepreneurial  $\bullet$  global

## **ENCODER** 4-to-2 ENCODER

### 4-to-2 Encoder consists of 4 inputs and 2 outputs.

Function:

$A_1A_0 = 00$  when  $D_3D_2D_1D_0 = 1110$   $A_1A_0 = 01$  when  $D_3D_2D_1D_0 = 1101$   $A_1A_0 = 10$  when  $D_3D_2D_1D_0 = 1011$   $A_1A_0 = 11$  when  $D_3D_2D_1D_0 = 0111$ Which implies:  $A_1 = D_3\overline{D_2}D_1D_0 + \overline{D_3}D_2D_1D_0$  $A_0 = D_3D_2\overline{D_1}D_0 + \overline{D_3}D_2D_1D_0$

4-to-2 Active Low Encoder

\*\*What happens if more than 1 input is '0' ( $D_1 = 0$  and  $D_2 = 0$ )?

$A_1A_0 = 11$  ERROR

We need a Priority Encoder

| <u>e</u>     |       | Inp   | Outputs |       |       |       |

|--------------|-------|-------|---------|-------|-------|-------|

| <b>Table</b> | $D_3$ | $D_2$ | $D_1$   | $D_0$ | $A_1$ | $A_0$ |

| L            | 1     | 1     | 1       | 0     | 0     | 0     |

| ctio         | 1     | 1     | 0       | 1     | 0     | 1     |

| nnc          | 1     | 0     | 1       | 1     | 1     | 0     |

| ц            | 0     | 1     | 1       | 1     | 1     | 1     |

## **ENCODER** PRIORITY ENCODER

Priority Encoder: Outputs depends on largest active input.

**Function**: Lowest Priority  $A_1A_0 = 00$  when  $D_3D_2D_1D_0 = 1110$ A0  $A_1A_0 = 01$  when  $D_3D_2D_1D_0 = 110X$ A1 dD1  $A_1A_0 = 10$  when  $D_3D_2D_1D_0 = 10XX$  $A_1A_0 = 11$  when  $D_3D_2D_1D_0 = 0XXX$ D2 Which implies: D3  $A_1 = D_3 \overline{D_2} D_1 D_0 + \overline{D_3} D_2 D_1 D_0$ Highest  $A_0 = D_3 D_2 \overline{D_1} D_0 + \overline{D_3} D_2 D_1 D_0$ Priority

### 4-to-2 Active Low Priority Encoder

\*\*What happens if more than 1 input is '0' (D0 = 0 and D1 = 0)?

Output  $A_1A_0 = 01$

| <u>e</u> |       | Inp   | Outputs |       |       |       |

|----------|-------|-------|---------|-------|-------|-------|

| [ab]     | $D_3$ | $D_2$ | $D_1$   | $D_0$ | $A_1$ | $A_0$ |

| L        | 1     | 1     | 1       | 0     | 0     | 0     |

| ctio     | 1     | 1     | 0       | Х     | 0     | 1     |

| nnc      | 1     | 0     | Х       | Х     | 1     | 0     |

| ц        | 0     | Х     | Х       | Х     | 1     | 1     |

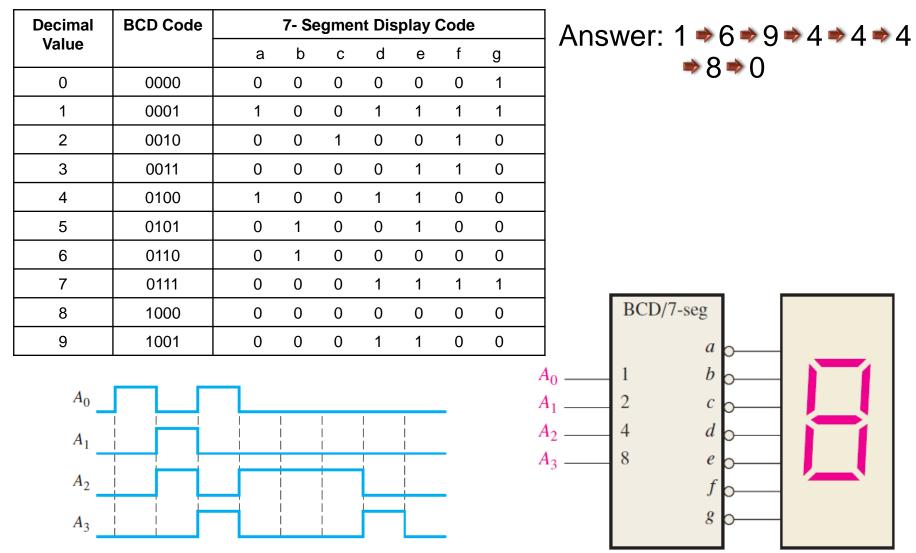

# BCD TO 7 SEGMENT DISPLAY DECODER

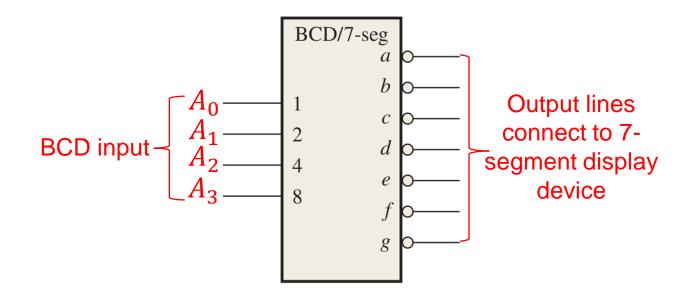

# BCD TO 7 SEGMENT DECODER OUTMALAYSIA

BCD to 7 segment decoder accept BCD codes on it inputs, and provides outputs to drive 7-segment display to produce decimal read out.

Logic symbol for BCD to 7segment decoder with Active-Low output

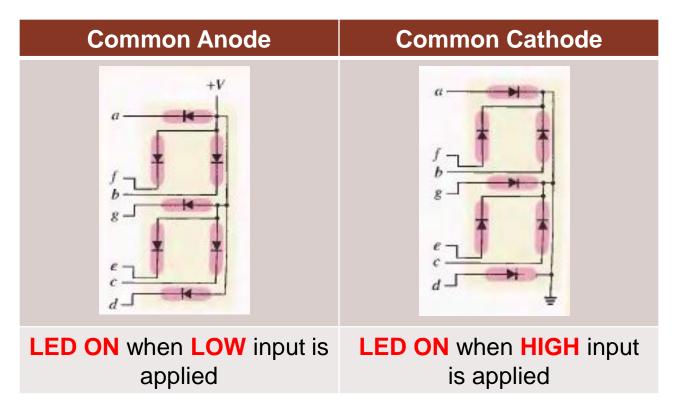

# BCD TO 7 SEGMENT DECODER 5 UTM INTRODUCTION

- Two type of 7-segment display;

- 1. Common Anode.

- 2. Common Cathode.

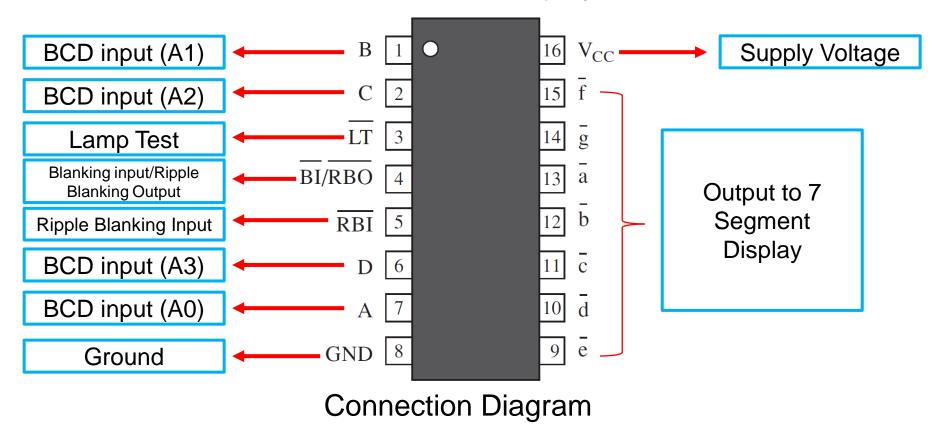

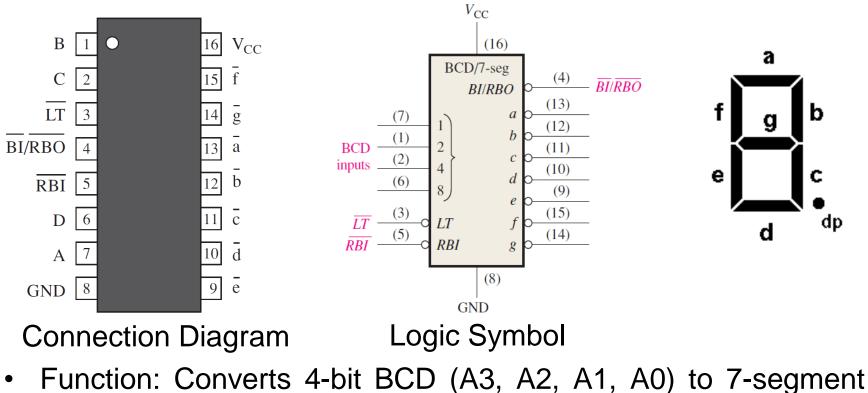

# BCD TO 7 SEGMENT DECODER OUTMALAYSIA INTRODUCTION: 74x47 IC

- The **74x47** is example of IC device that decodes a BCD input and drives the 7-segment display.

- The 74x47 is a common anode displays.

# BCD TO 7 SEGMENT DECODER OUTMALAYSA INTRODUCTION: 74x47 IC

- The **74x47** is example of IC device that decodes a BCD input and drives the 7-segment display.

- The 74x47 is a common anode displays.

Function: Converts 4-bit BCD (A3, A2, A1, A0) to 7-segment LED (a, b, c, d, e, f, g)

# **BCD TO 7 SEGMENT DECODER**

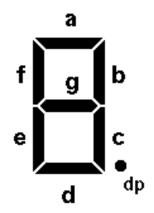

|             | Decimal |      |   | 7- Segment Display Code |   |   |   |   |   |  |  |

|-------------|---------|------|---|-------------------------|---|---|---|---|---|--|--|

|             | Value   | Code | а | b                       | С | d | е | f | g |  |  |

|             | 0       | 0000 | 0 | 0                       | 0 | 0 | 0 | 0 | 1 |  |  |

|             | 1       | 0001 | 1 | 0                       | 0 | 1 | 1 | 1 | 1 |  |  |

| ble         | 2       | 0010 | 0 | 0                       | 1 | 0 | 0 | 1 | 0 |  |  |

| Truth Table | 3       | 0011 | 0 | 0                       | 0 | 0 | 1 | 1 | 0 |  |  |

| uth         | 4       | 0100 | 1 | 0                       | 0 | 1 | 1 | 0 | 0 |  |  |

| Г           | 5       | 0101 | 0 | 1                       | 0 | 0 | 1 | 0 | 0 |  |  |

|             | 6       | 0110 | 0 | 1                       | 0 | 0 | 0 | 0 | 0 |  |  |

|             | 7       | 0111 | 0 | 0                       | 0 | 1 | 1 | 1 | 1 |  |  |

|             | 8       | 1000 | 0 | 0                       | 0 | 0 | 0 | 0 | 0 |  |  |

| a           | 9       | 1001 | 0 | 0                       | 0 | 1 | 1 | 0 | 0 |  |  |

Segments turn on and off to display different numbers

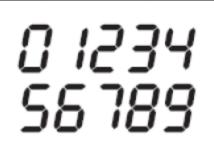

# BCD TO 7 SEGMENT DECODER 5 UTM EXAMPLE

A 7-segment decoder drives the display as figure below. If waveforms are applied as indicated, determine the sequence of digits that appears on display.

# BCD TO 7 SEGMENT DECODER 5 UT EXAMPLE

# ADDERS

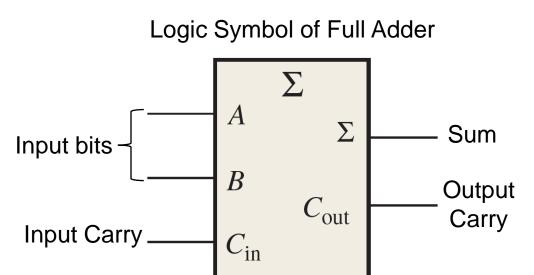

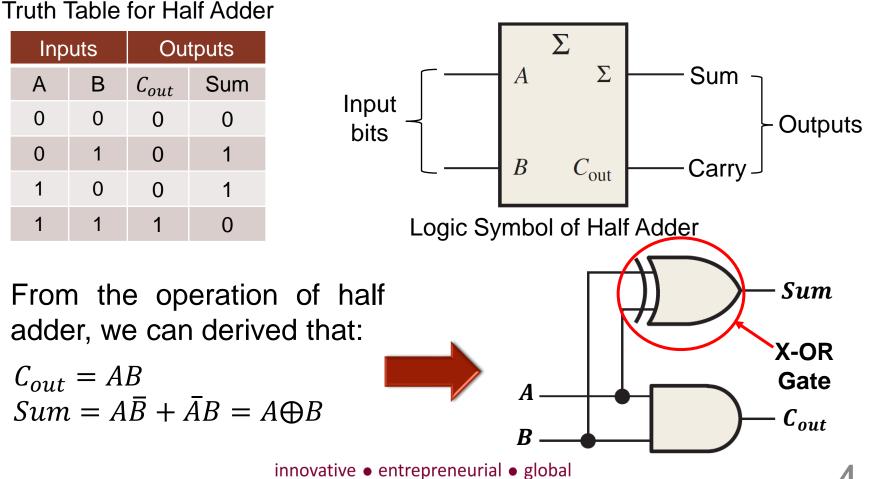

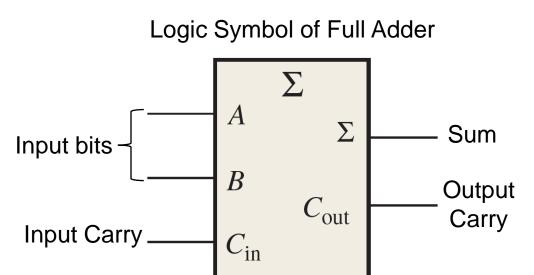

## ADDERS & COMPARATOR ADDERS: INTRODUCTION

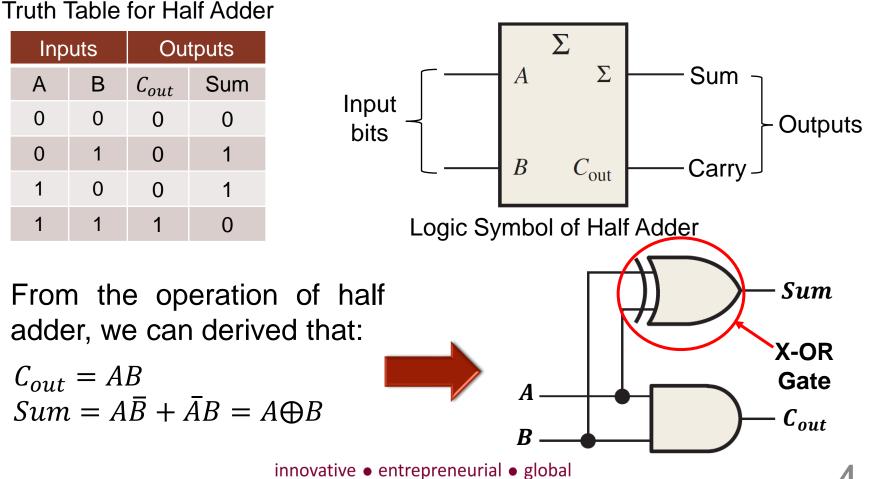

Adders combine two operand arithmetically using binary addition rules.

Half Adder accepts two binary digits on its inputs and produce two binary digits on its outputs, sum bit and carry bit.

Inputs Outputs Sum Α В  $C_{out}$

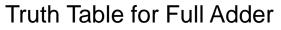

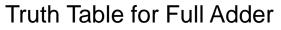

Full Adder accepts two inputs bits & input carry and generate sum output & output carry.

|   | Inputs | Outputs         |      |     |

|---|--------|-----------------|------|-----|

| А | В      | C <sub>in</sub> | Cout | Sum |

| 0 | 0      | 0               | 0    | 0   |

| 0 | 0      | 1               | 0    | 1   |

| 0 | 1      | 0               | 0    | 1   |

| 0 | 1      | 1               | 1    | 0   |

| 1 | 0      | 0               | 0    | 1   |

| 1 | 0      | 1               | 1    | 0   |

| 1 | 1      | 0               | 1    | 0   |

| 1 | 1      | 1               | 1    | 1   |

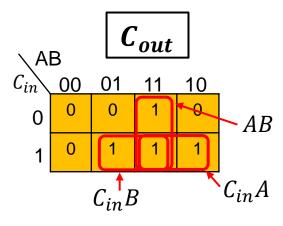

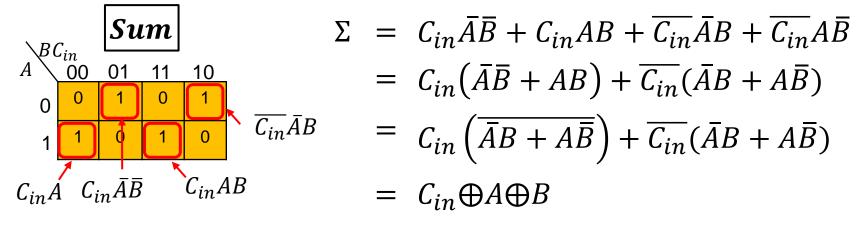

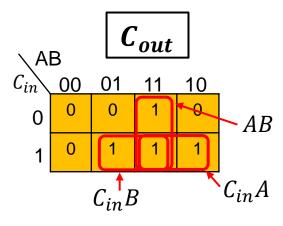

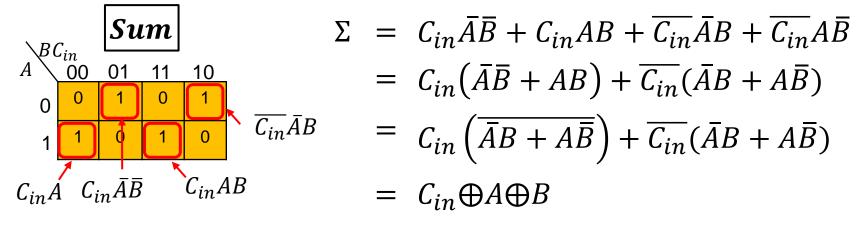

From the operation of Full Adder, we can derives Boolean equation of Cout and Sum using K-map.

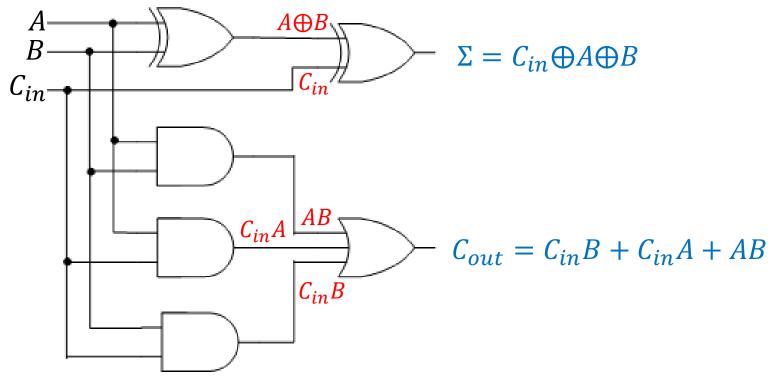

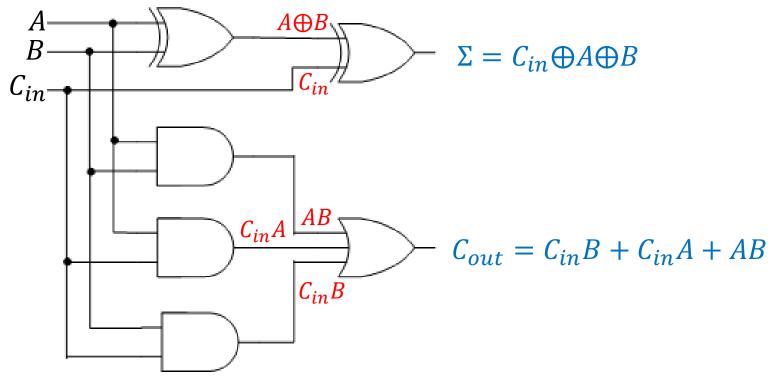

$$C_{out} = C_{in}B + C_{in}A + AB$$

• Logic circuit of Full Adder:

Logic Circuit of Full Adder

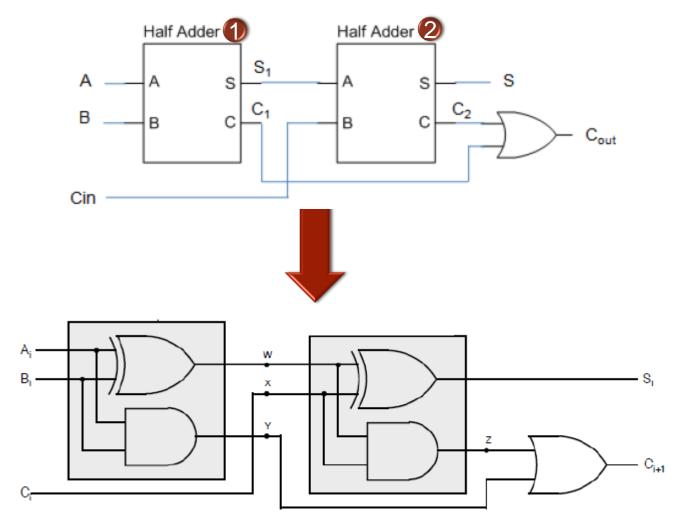

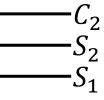

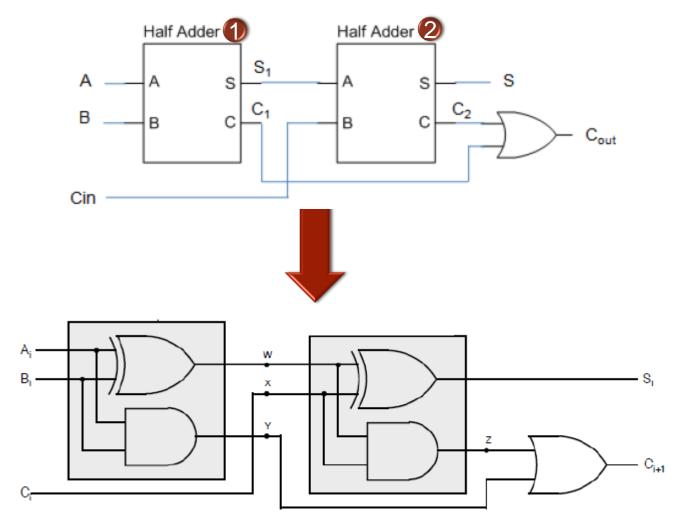

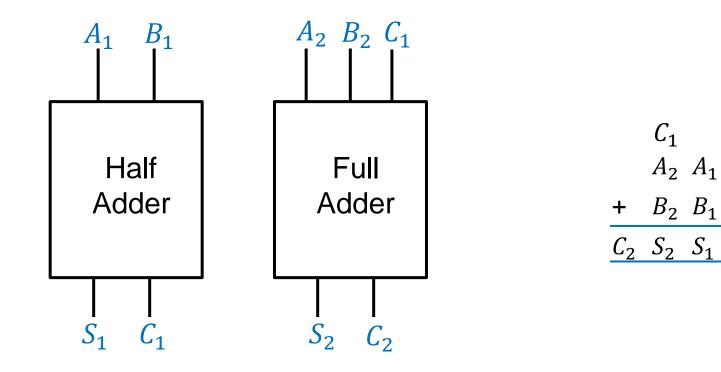

• How to design Full Adder using Half Adder?

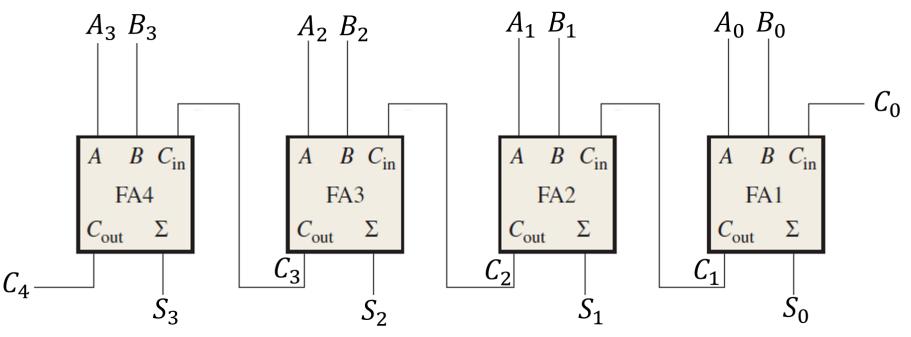

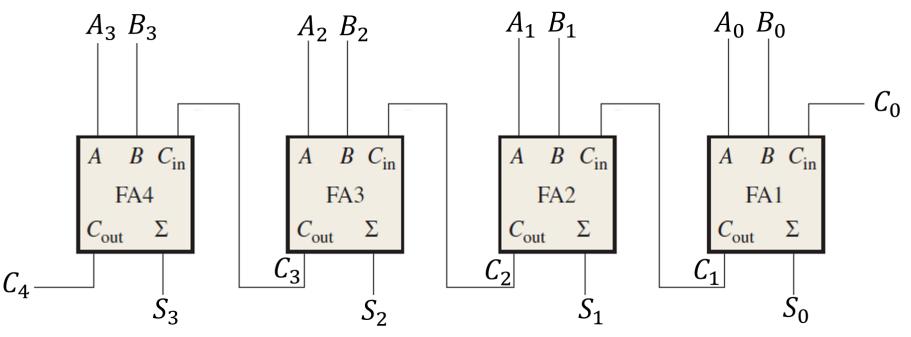

# ADDERS & COMPARATOR ADDERS: RIPPLE CARRY ADDER

- **Ripple Carry Adder** is used to add multiple bit binary numbers.

- The carry-out output from a state is connected to the carry-in input of the next state.

- To design 4-bit ripple carry adder, we need 4 full adders.

- Input =  $A_3A_2A_1A_0$ ,  $B_3B_2B_1B_0$  and  $C_0$  ( $C_0$  initially set to 0).

- Output =  $S_3 S_2 S_1 S_0$  and  $C_4$ .

## ADDERS & COMPARATOR ADDERS: RIPPLE CARRY ADDER

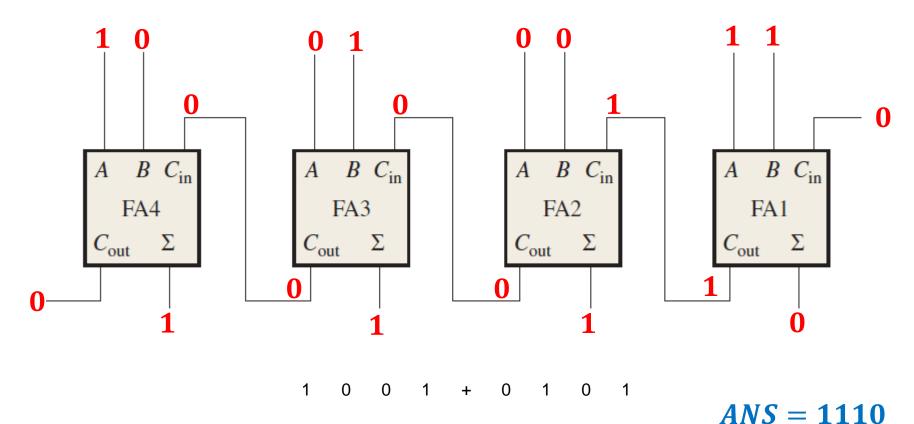

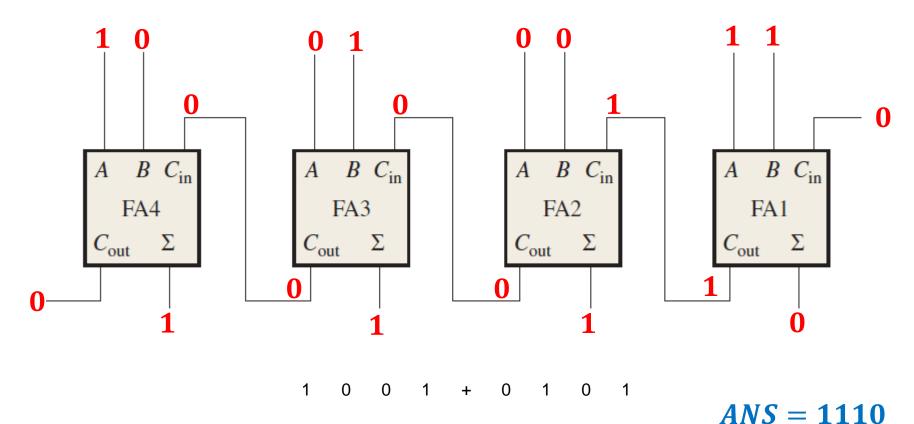

Example 1

1001 + 0101

$A_3 A_2 A_1 A_0 \qquad B_3 B_2 B_1 B_0$

innovative • entrepreneurial • global

10

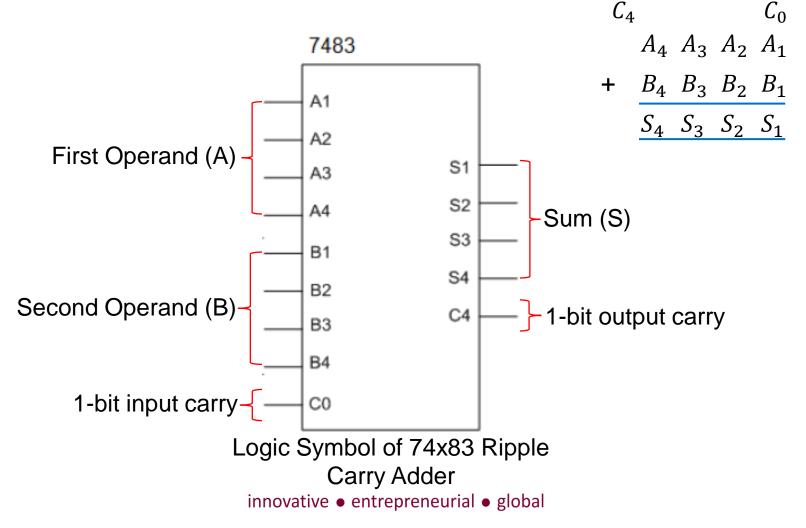

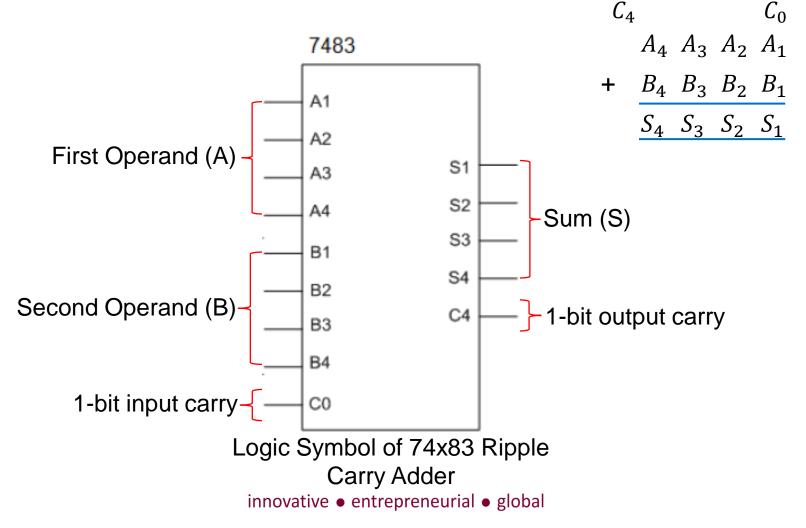

The 74x83 is an example of IC device for faster 4-bit ripple carry adder.

#### Example 2

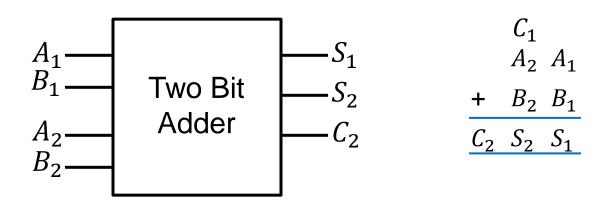

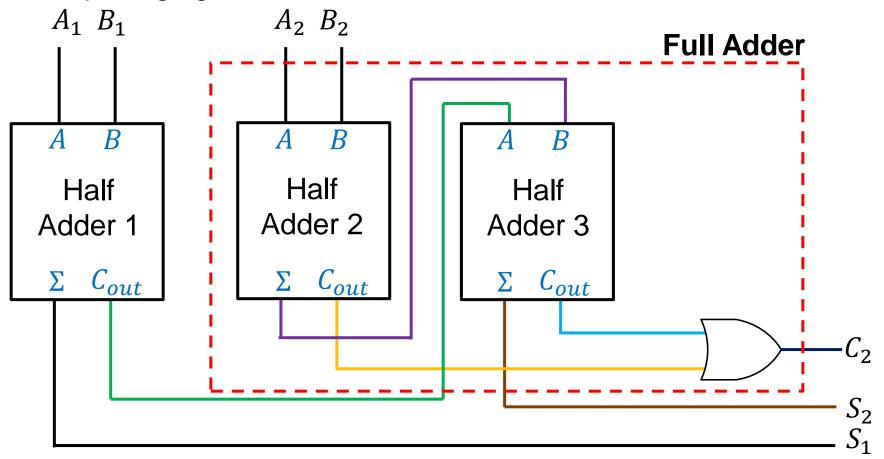

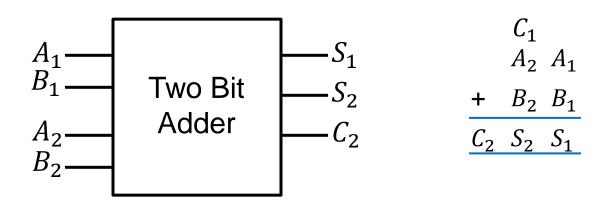

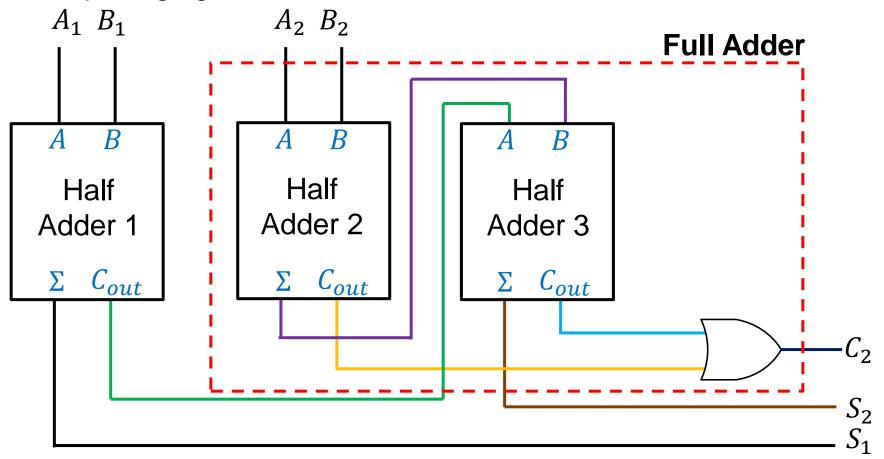

Figure below shows the block diagram of a two bits adder A2A1 and B2B1 addition. The result should be in three bits binary number C2S2S1. Obtain the truth table for output C2, S2 and S1.

#### Example 2

Figure below shows the block diagram of a two bits adder A2A1 and B2B1 addition. The result should be in three bits binary number C2S2S1. Obtain the truth table for output C2, S2 and S1.

|    | In | put | Output |    |    |    | In | put | Output |    |    |    |    |

|----|----|-----|--------|----|----|----|----|-----|--------|----|----|----|----|

| A2 | A1 | B2  | B1     | C2 | S2 | S1 | A2 | A1  | B2     | B1 | C2 | S2 | S1 |

| 0  | 0  | 0   | 0      | 0  | 0  | 0  | 1  | 0   | 0      | 0  | 0  | 1  | 0  |

| 0  | 0  | 0   | 1      | 0  | 0  | 1  | 1  | 0   | 0      | 1  | 0  | 1  | 1  |

| 0  | 0  | 1   | 0      | 0  | 1  | 0  | 1  | 0   | 1      | 0  | 1  | 0  | 0  |

| 0  | 0  | 1   | 1      | 0  | 1  | 1  | 1  | 0   | 1      | 1  | 1  | 0  | 1  |

| 0  | 1  | 0   | 0      | 0  | 0  | 1  | 1  | 1   | 0      | 0  | 0  | 1  | 1  |

| 0  | 1  | 0   | 1      | 0  | 1  | 0  | 1  | 1   | 0      | 1  | 1  | 0  | 0  |

| 0  | 1  | 1   | 0      | 0  | 1  | 1  | 1  | 1   | 1      | 0  | 1  | 0  | 1  |

| 0  | 1  | 1   | 1      | 1  | 0  | 0  | 1  | 1   | 1      | 1  | 1  | 1  | 0  |

#### **Truth Table for 2 bits Binary Addition**

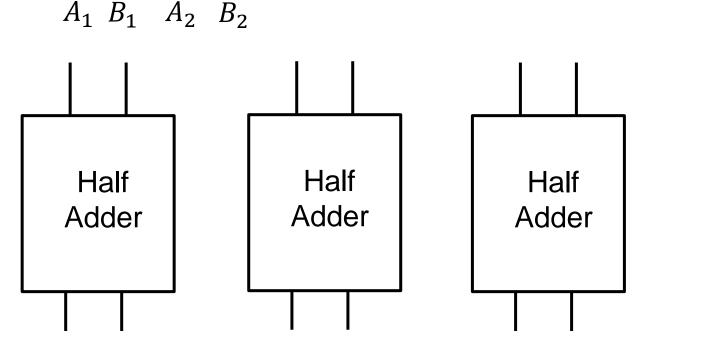

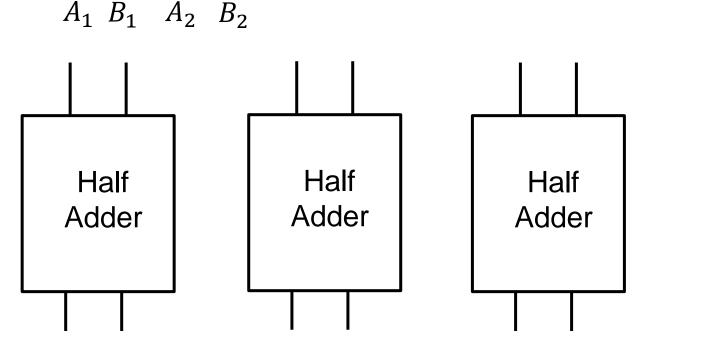

#### Example 2(cont.)

#### Example 2(cont.)

#### Example 2(cont.)

# ADDERS

innovative • entrepreneurial • global

#### ADDERS & COMPARATOR ADDERS: INTRODUCTION

Adders combine two operand arithmetically using binary addition rules.

Half Adder accepts two binary digits on its inputs and produce two binary digits on its outputs, sum bit and carry bit.

Inputs Outputs Sum Α В  $C_{out}$

Full Adder accepts two inputs bits & input carry and generate sum output & output carry.

|   | Inputs | Outputs         |      |     |  |  |

|---|--------|-----------------|------|-----|--|--|

| А | В      | C <sub>in</sub> | Cout | Sum |  |  |

| 0 | 0      | 0               | 0    | 0   |  |  |

| 0 | 0      | 1               | 0    | 1   |  |  |

| 0 | 1      | 0               | 0    | 1   |  |  |

| 0 | 1      | 1               | 1    | 0   |  |  |

| 1 | 0      | 0               | 0    | 1   |  |  |

| 1 | 0      | 1               | 1    | 0   |  |  |

| 1 | 1      | 0               | 1    | 0   |  |  |

| 1 | 1      | 1               | 1    | 1   |  |  |

From the operation of Full Adder, we can derives Boolean equation of Cout and Sum using K-map.

$$C_{out} = C_{in}B + C_{in}A + AB$$

innovative • entrepreneurial • global

• Logic circuit of Full Adder:

Logic Circuit of Full Adder

• How to design Full Adder using Half Adder?

- **Ripple Carry Adder** is used to add multiple bit binary numbers.

- The carry-out output from a state is connected to the carry-in input of the next state.

- To design 4-bit ripple carry adder, we need 4 full adders.

- Input =  $A_3A_2A_1A_0$ ,  $B_3B_2B_1B_0$  and  $C_0$  ( $C_0$  initially set to 0).

- Output =  $S_3 S_2 S_1 S_0$  and  $C_4$ .

innovative • entrepreneurial • global

Example 1

1001 + 0101

$A_3 A_2 A_1 A_0 \qquad B_3 B_2 B_1 B_0$

innovative • entrepreneurial • global

10

The 74x83 is an example of IC device for faster 4-bit ripple carry adder.

#### Example 2

Figure below shows the block diagram of a two bits adder A2A1 and B2B1 addition. The result should be in three bits binary number C2S2S1. Obtain the truth table for output C2, S2 and S1.

#### Example 2

Figure below shows the block diagram of a two bits adder A2A1 and B2B1 addition. The result should be in three bits binary number C2S2S1. Obtain the truth table for output C2, S2 and S1.

|    | In | put | Output |    |    |    | In | put | Output |    |    |    |    |

|----|----|-----|--------|----|----|----|----|-----|--------|----|----|----|----|

| A2 | A1 | B2  | B1     | C2 | S2 | S1 | A2 | A1  | B2     | B1 | C2 | S2 | S1 |

| 0  | 0  | 0   | 0      | 0  | 0  | 0  | 1  | 0   | 0      | 0  | 0  | 1  | 0  |

| 0  | 0  | 0   | 1      | 0  | 0  | 1  | 1  | 0   | 0      | 1  | 0  | 1  | 1  |

| 0  | 0  | 1   | 0      | 0  | 1  | 0  | 1  | 0   | 1      | 0  | 1  | 0  | 0  |

| 0  | 0  | 1   | 1      | 0  | 1  | 1  | 1  | 0   | 1      | 1  | 1  | 0  | 1  |

| 0  | 1  | 0   | 0      | 0  | 0  | 1  | 1  | 1   | 0      | 0  | 0  | 1  | 1  |

| 0  | 1  | 0   | 1      | 0  | 1  | 0  | 1  | 1   | 0      | 1  | 1  | 0  | 0  |

| 0  | 1  | 1   | 0      | 0  | 1  | 1  | 1  | 1   | 1      | 0  | 1  | 0  | 1  |

| 0  | 1  | 1   | 1      | 1  | 0  | 0  | 1  | 1   | 1      | 1  | 1  | 1  | 0  |

#### **Truth Table for 2 bits Binary Addition**

#### Example 2(cont.)

#### Example 2(cont.)

#### Example 2(cont.)

# COMPARATOR

innovative • entrepreneurial • global

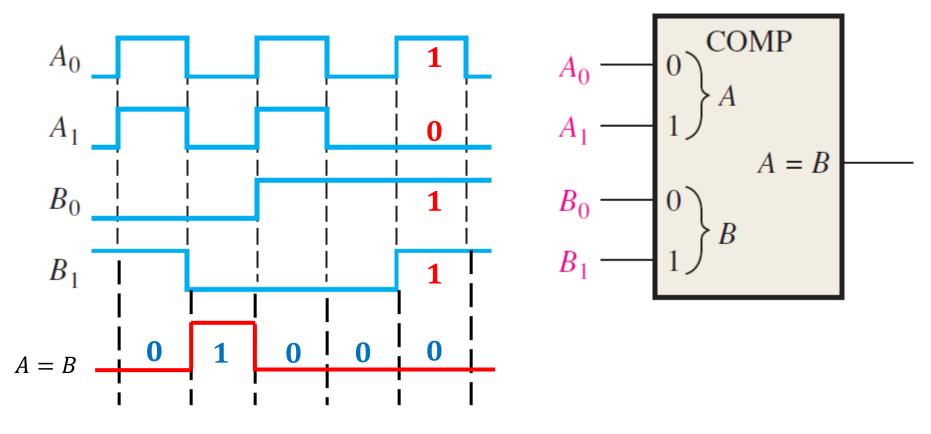

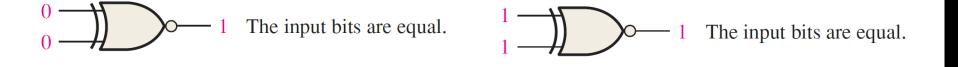

#### **ADDERS & COMPARATOR** COMPARATOR: EQUALITY

- Comparator is used to compare the magnitude of two binary quantities to determine the relationship of those quantities.

- As learned in Chapter 3, the exclusive-NOR gate can be used as a basic comparator.

$$A=0$$

$$B=0$$

$$1$$

$S = \overline{\overline{A} \cdot B} + A \cdot \overline{\overline{B}} = \overline{\overline{0} \cdot 0} + 0 \cdot \overline{\overline{0}} = \overline{1 \cdot 0} + 0 \cdot \overline{1} = \overline{0} = 1$

#### ADDERS & COMPARATOR COMPARATOR: EQUALITY

- Comparator is used to compare the magnitude of two binary quantities to determine the relationship of those quantities.

- As learned in Chapter 3, the exclusive-NOR gate can be used as a basic comparator.

$$A=0$$

$$B=1$$

$$0$$

$$S = \overline{\overline{A} \cdot B} + A \cdot \overline{\overline{B}} = \overline{\overline{0} \cdot 1} + 1 \cdot \overline{\overline{0}} = \overline{1 \cdot 1} + 1 \cdot \overline{1} = \overline{1} = 0$$

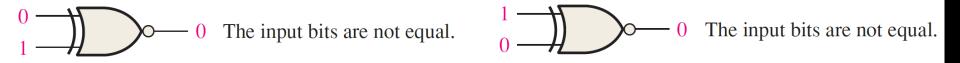

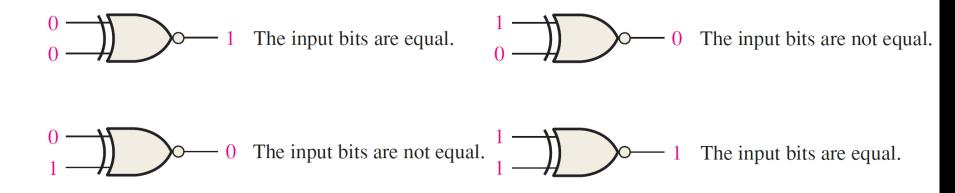

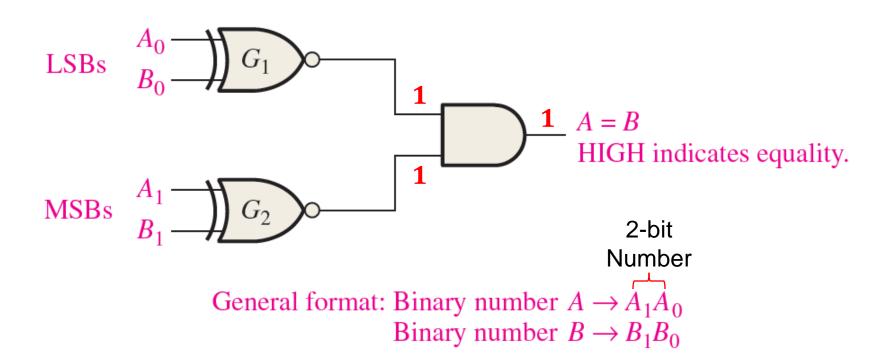

### ADDERS & COMPARATOR COMPARATOR: EQUALITY

- Comparator is used to compare the magnitude of two binary quantities to determine the relationship of those quantities.

- As learned in Chapter 3, the exclusive-NOR gate can be used as a basic comparator.

In order to compare binary number containing two each bits, an additional excusive-NOR, NOT and AND gate are necessary.

• The output indicate (1) is equality while (0) is inequality.

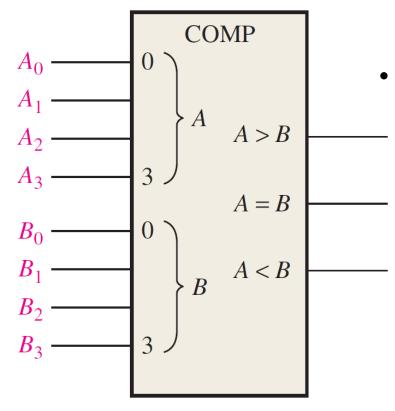

### ADDERS & COMPARATOR COMPARATOR: INEQUALITY

- In addition to equality output, many IC comparators (74x85) provide additional outputs that indicate which of the two binary numbers being compared is the larger.

- That is, (A > B) & (A < B).

- To determine inequality of numbers

A and B, first examine the highest

order bit in each number:

- If  $A_3 = 1$  and  $B_3 = 0$ ; A > B

- If  $A_3 = 0$  and  $B_3 = 1$ ; A < B

- If  $A_3 = B_3$ ; then examine the next lower bit position for an inequality.

#### **ADDERS & COMPARATOR** COMPARATOR: INEQUALITY

• The truth table for **74x85 comparator**.

| A <sub>1</sub> | A | <sub>0</sub> B <sub>1</sub> | B <sub>0</sub> | $\begin{array}{c} A = B \\ (F_1) \end{array}$ | A > B<br>(F <sub>2</sub> ) | A < B<br>(F <sub>3</sub> ) | A <sub>1</sub> | A | <sub>o</sub> B <sub>1</sub> | B <sub>0</sub> | $\begin{array}{c} A = B \\ (F_1) \end{array}$ | A > B<br>(F <sub>2</sub> ) | A < B<br>(F <sub>3</sub> ) |

|----------------|---|-----------------------------|----------------|-----------------------------------------------|----------------------------|----------------------------|----------------|---|-----------------------------|----------------|-----------------------------------------------|----------------------------|----------------------------|

| 0              | 0 | 0                           | 0              | 1                                             | 0                          | 0                          | 1              | 0 | 0                           | 0              | 0                                             | 1                          | 0                          |

| 0              | 0 | 0                           | 1              | 0                                             | 0                          | 1                          | 1              | 0 | 0                           | 1              | 0                                             | 1                          | 0                          |

| 0              | 0 | 1                           | 0              | 0                                             | 0                          | 1                          | 1              | 0 | 1                           | 0              | 1                                             | 0                          | 0                          |

| 0              | 0 | 1                           | 1              | 0                                             | 0                          | 1                          | 1              | 0 | 1                           | 1              | 0                                             | 0                          | 1                          |

| 0              | 1 | 0                           | 0              | 0                                             | 1                          | 0                          | 1              | 1 | 0                           | 0              | 0                                             | 1                          | 0                          |

| 0              | 1 | 0                           | 1              | 1                                             | 0                          | 0                          | 1              | 1 | 0                           | 1              | 0                                             | 1                          | 0                          |

| 0              | 1 | 1                           | 0              | 0                                             | 0                          | 1                          | 1              | 1 | 1                           | 0              | 0                                             | 1                          | 0                          |

| 0              | 1 | 1                           | 1              | 0                                             | 0                          | 1                          | 1              | 1 | 1                           | 1              | 1                                             | 0                          | 0                          |

#### ADDERS & COMPARATOR COMPARATOR: INEQUALITY

- By using K-map, expression of F1, F2 and F3 are obtained as follows

- For A = B:

$F_1 = \overline{A_1} \cdot \overline{A_0} \cdot \overline{B_1} \cdot \overline{B_0} + \overline{A_1} \cdot A_0 \cdot \overline{B_1} \cdot B_0 + A_1 \cdot \overline{A_0} \cdot B_1 \cdot \overline{B_0} + A_1 \cdot A_0 \cdot B_1 \cdot B_0$

For A > B:  $F_1 = A_1 \cdot \overline{B_1} + A_0 \cdot \overline{B_1} \cdot \overline{B_0} + A_1 \cdot A_0 \cdot \overline{B_0}$

For A < B:  $F_1 = \overline{A_1} \cdot B_1 + \overline{A_0} \cdot B_1 \cdot B_0 + \overline{A_1} \cdot \overline{A_0} \cdot B_0$

#### Example 4

The waveform are applied to comparator as shown. Determine the output (A = B) waveform.