# SEE 1223 DIGITAL ELECTRONICS CHAPTER 9: PROGRAMMABLE LOGIC

#### DR. MOHD SAIFUL AZIMI BIN MAHMUD

P19a-04-03-30 School of Electrical Engineering Faculty of Engineering Universiti Teknologi Malaysia 019-7112948 azimi@utm.my

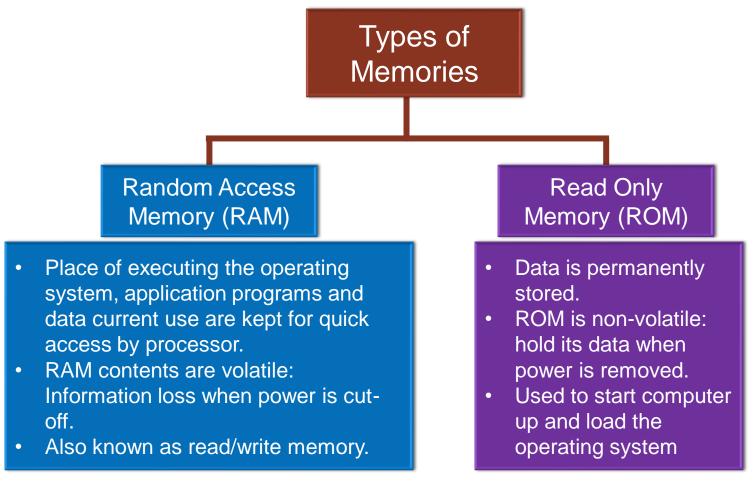

# MEMORY: RAM & ROM

## **MEMORY** INTRODUCTION

Memories are devices to which information is transferred for storage and from which information is available for processing.

#### UTTM UNIVERSITI TEKNOLOGI MALAYSIA

## MEMORY RAM

- Integrated circuit RAM devices are available in two variations:

- 1. Static RAM (SRAM)

- Consist of internal latches that store the binary information.

- Stored information remains valid as long as power is applied to the unit.

- Faster.

- High power consumption.

- Expensive.

### 2. Dynamic RAM (DRAM)

- Stores binary information in the form of electric charges on capacitors provided by MOS transistors.

- The charge of capacitors tend to decay with time, thus need to periodically recharge by refreshing the dynamic memory every few milliseconds.

- Reduce power consumption.

- Large number of memory words per chip.

## MEMORY ROM

• Various types of ROM:

### 1. Mask Programmed ROM (MROM)

- Programmed using a mask during fabrication by manufacturer.

- Advantages: high speed, high density, low unit costs.

- Disadvantage: contents are permanent.

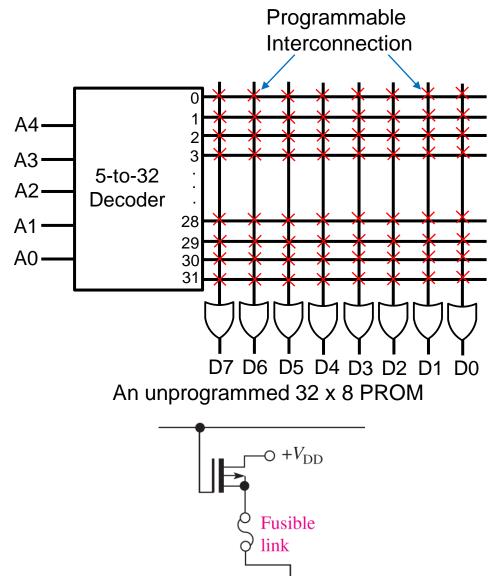

### 2. Programmable ROM (PROM)

- Contents are in the form fuses which are blown during programming.

- Once blown, the fuses cannot be restored.

- PROM is one time programmable (OTP): cannot be updated and reused after initial programming.

### MEMORY ROM

## MEMORY ROM

• Various types of ROM (cont.):

### 3. Erasable Programmable ROM (EPROM)

- Can be erased and reprogrammed many times.

- The whole chip is erased by exposure to approximately 20 minutes of intense UV light.

- 4. Electrically-Erasable Programmable ROM (EEPROM)

- Can be erased and reprogrammed without requiring special burning equipment.

- High costs.

- Allows only one memory word to be written or erased at any one time.

### 5. Flash Memory

- High speed and high density.

- Erases many locations simultaneously.

- Can only tolerate about 10000 erase operations before the device fails.

#### innovative • entrepreneurial • global

### MEMORY ROM

### Example

Given the truth table of 8 x 4 ROM as follows. Find the number of programmable interconnections & implements the ROM circuit.

|    |    |    |    |    |    |    | Number of programmable interconnection:                                                                                                  |

|----|----|----|----|----|----|----|------------------------------------------------------------------------------------------------------------------------------------------|

| A2 | A1 | A0 | D3 | D2 | D1 | D0 | $= 8 \times 4 = 32$                                                                                                                      |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  |                                                                                                                                          |

| 0  | 0  | 1  | 0  | 0  | 0  | 0  |                                                                                                                                          |

| 0  | 1  | 0  | 0  | 0  | 0  | 1  | A2 1 2 41 3-to-83                                                                                                                        |

| 0  | 1  | 1  | 0  | 0  | 1  | 0  | A1 3-10-8 3<br>A0 Decoder 4                                                                                                              |

| 1  | 0  | 0  | 0  | 1  | 0  | 0  |                                                                                                                                          |

| 1  | 0  | 1  | 0  | 1  | 1  | 0  |                                                                                                                                          |

| 1  | 1  | 0  | 1  | 0  | 0  | 1  |                                                                                                                                          |

| 1  | 1  | 1  | 1  | 1  | 0  | 0  | $1 \qquad \qquad$ |

|    |    |    |    |    |    |    | D3 D2 D1 D0                                                                                                                              |

# PROGRAMMABLE LOGIC DEVICE: PLA & PAL

# PROGRAMMABLE LOGIC DEVICE (PLD) INTRODUCTION

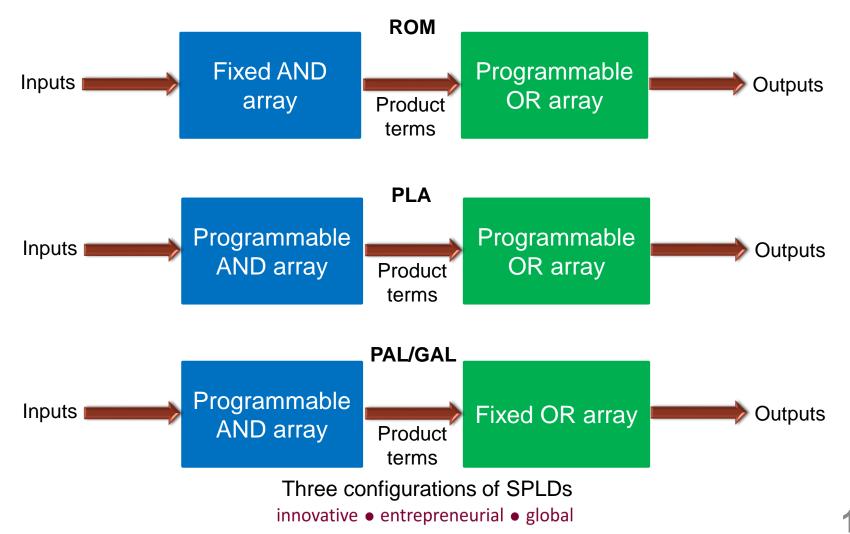

- PLD consists of general purpose logic resources that can be connected according to the engineer's design.

- It must be programmed first before be used in circuit.

- Advantages: Fewer parts needed, reduce inventory cost, number of interconnections are decreases as more logic integrated into each chip, higher reliability.

- **Disadvantages:** Longer propagation delay, high power consumption.

- Example of PLD are:

- ROM

- PLA

- PAL

- GAL

# PROGRAMMABLE LOGIC DEVICE (PLD) INTRODUCTION

# PROGRAMMABLE LOGIC DEVICE (PLD)

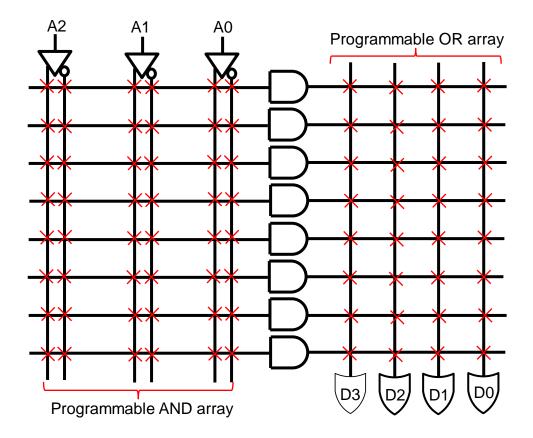

### PLA

- Programmable Logic Array (PLA) consists of programmable AND and OR arrays.

- Advantageous when

- Relatively few unique minterm combinations.

- Many minterms are shared among the output functions.

### Drawbacks

- Expensive to manufacture.

- Poor speed performance: Thus PAL (Programmable Array Logic) and GAL (Generic Array Logic) were introduced.

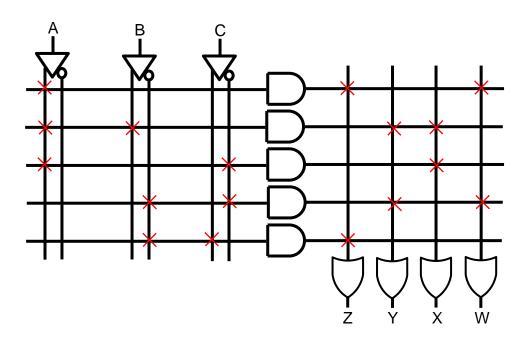

# PROGRAMMABLE LOGIC DEVICE (PLD) PLA

× Programmable Interconnection

# PROGRAMMABLE LOGIC DEVICE (PLD)

### PLA

### Example

Implement the following logic function using PLA.

$W = A + \overline{B}\overline{C}$  $X = A\overline{C} + AB$  $Y = \overline{B}\overline{C} + AB$  $Z = \overline{B}\overline{C} + A$

# PROGRAMMABLE LOGIC DEVICE (PLD)

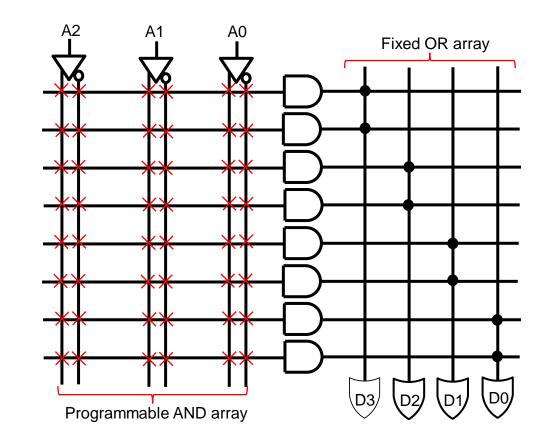

### PAL

- Programmable Array Logic (PAL) provides an array of programmable AND gates, but the OR connections are fixed.

- Unlike PLA, product term cannot be shared among gates.

- Advantageous when

- Cheaper and faster.

### GAL

- Generic Array Logic (GAL) has the same basic structure as PAL (Programmable AND Gates, OR connections are fixed), but being EEPROM-based: Can be erased and reprogrammed.

- **GAL** improves upon PAL in three aspects.

- Can be erased.

- Can be programmed while installed in circuit.

- Has programmable output stage or marcocells that has feedback to enable product term to be expanded and complementary output.

# PROGRAMMABLE LOGIC DEVICE (PLD) PAL/GAL

- × Programmable Interconnection

- Fixed Interconnection