#### SEEU2012 Electronics 20212022/2

#### Chapter 4 Bipolar Junction Transistor (BJT) DC Analysis

Dr. Nur Najahatul Huda Saris School of Electrical Engineering, Faculty of Engineering UNIVERSITI TEKNOLOGI MALAYSIA nurnajahatulhuda@utm.my

innovative • entrepreneurial • global

### **Course Learning Outcomes**

Apply the basic law and theorems of electronic devices to describe their basic operation.

Apply the basic law, theorems and methods of analysis to solve complex problem related to circuitry.

3

Work in a team and communicate effectively.

- i. Describe the basic structure of a BJT.

- ii. Explain and analyze basic BJT bias and operation.

- iii. Discuss on the function of a BJT as an amplifier.

- iv. Discuss the parameters and characteristic of a BJT and its application in electrical circuit.

#### What is Transistor?

□Transistors are solid state devices that is used for amplifying, controlling and generating electrical signal.

□Transistors are used widely in electronic equipment such as computers, calculators, radios and communication satellite.

#### What is Transistor?

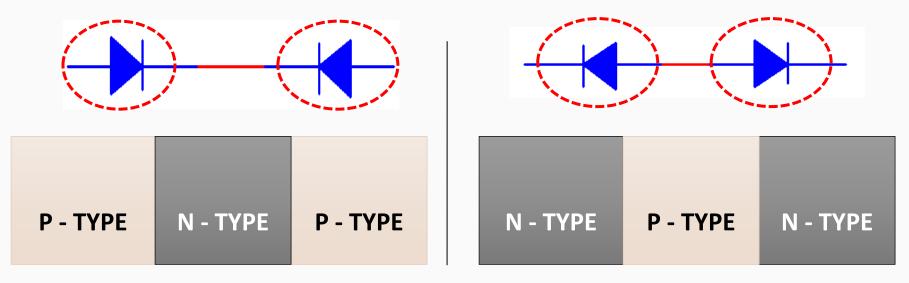

Two basic types of transistor is bipolar junction transistor (BJT) and Field Effect Transistor (FET).

□ Transistor is like 2 diodes connected.

□ Each region have different doping concentration.

□ Transistor is widely been used as switch and amplifier.

#### Introduction to BJT

BJT is bipolar because both majority and minority carriers take part in the current flow. (a) N-type - electrons as majority carrier (b) P-type – holes as majority carrier.

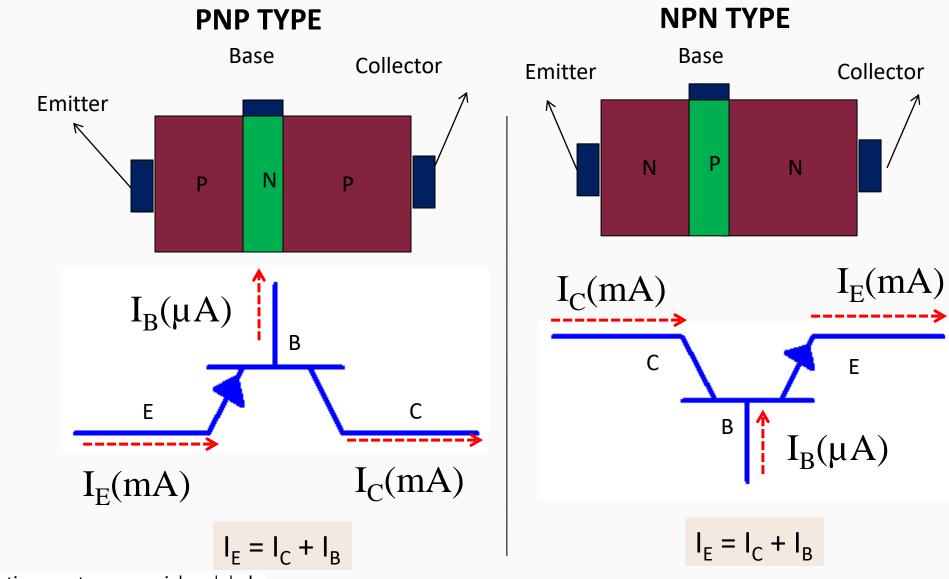

□2 types of BJT: (a) NPN and (b) PNP

**BJT** regions are:

- Emitter (E) send the carries into the base region and then into the collector.

- Base (B)act as control region. Carriers flow depending on the biased voltage.

- Collector (C) collects the carries.

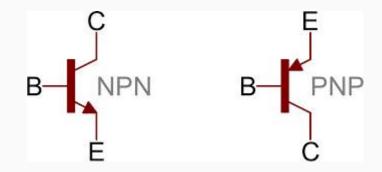

#### Structure & Symbol of BJT

innovative • entrepreneurial • global

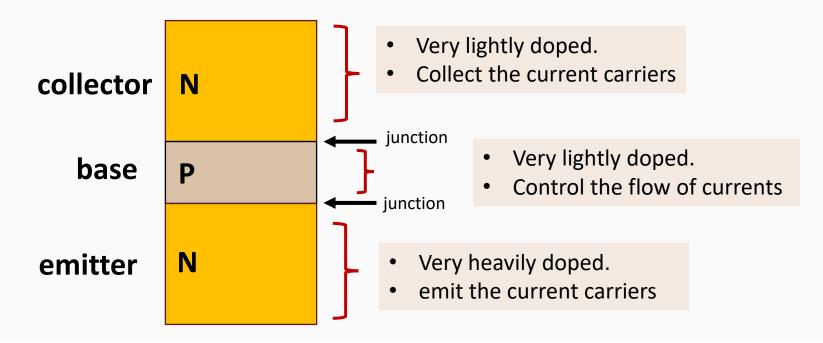

#### **NPN Transistor Structure**

- The emitter is rich in current carriers. It send the carriers into the base region and on to the collector.

- The collector collect the carriers.

- The emitter emits the carriers.

The base act as a control region. It can allow none, some or many carriers to flow from emitter to collector. innovative

entrepreneurial

global

#### BJT Characteristic & Parameters

$\Box \beta_{DC}$  – is the ratio of the DC collector current, I<sub>C</sub> to the DC base current, (I<sub>B</sub>)

Typical value range from less than 20 to 200 or higher.

$$\beta_{\rm DC} = \frac{I_{\rm C}}{I_{\rm B}}$$

$\Box \alpha_{DC}$  – is the ratio of the DC emitter current,  $I_E$  to the DC collector current,  $(I_C)$ .

The value range from 0.95 to 0.99 but always less than 1.

$$\alpha_{\rm DC} = \frac{I_{\rm C}}{I_{\rm E}} \qquad \beta = \left(\frac{\alpha}{1 - \alpha}\right)$$

#### BJT Behavior: Current-Voltage Characteristics

□ The behaviour of the transistor can be represented by current-voltage (I-V) curves (called the characteristic curves of the device).

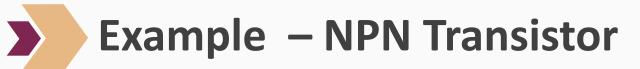

#### **Input Characteristics**

The relation between input current and input voltage for different values of output voltage

#### **Output Characteristics**

The relation between output current and output voltage for different values of input current

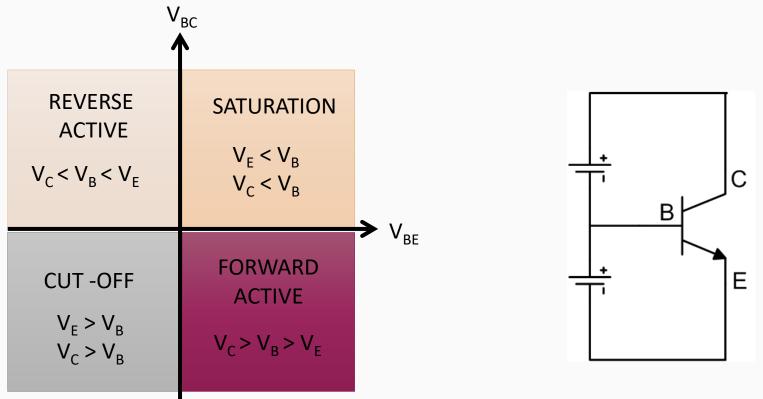

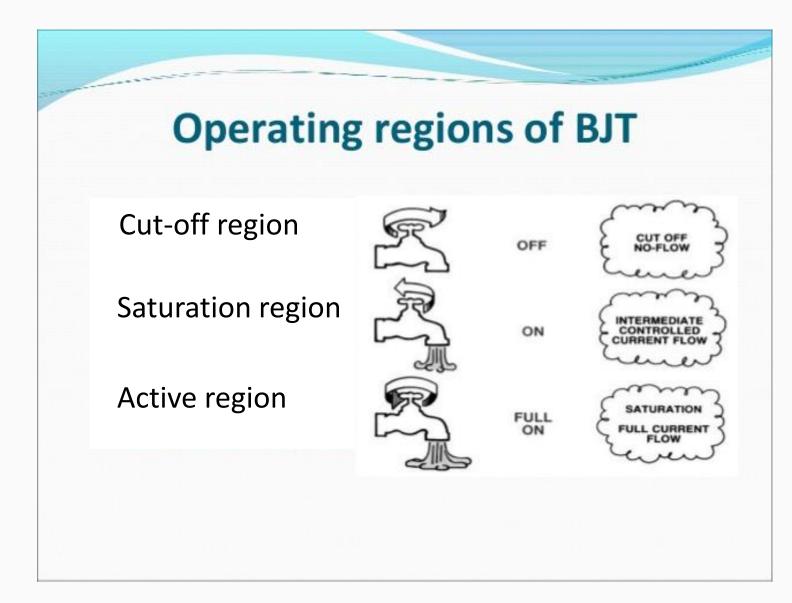

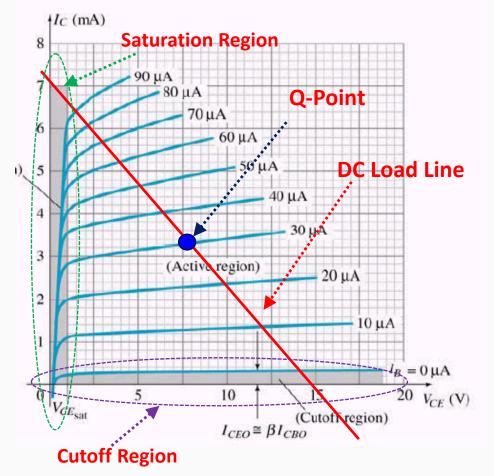

#### BJT Basic Operation Region

- To produce a desired mode of operation, the two P-N junctions must be correctly biased

- □NPN transistor will be used for illustrationThe operation of the PNP is the same as for the NPN except that

- the roles of the electrons and holes

- the bias voltage polarities

- the current directions are all reversed

- A single PN junction has two different types of bias: forward and reverse.

- □ Thus, a 2 PN junction device has four types of bias.

#### BJT Mode of Operation for NPN and PNP

Saturation and cut-off operations are important for digital circuits like switching.

Active region are important for amplifier application.

| Base -Emitter<br>Junction | Base - Collector<br>Junction | Operating Region |

|---------------------------|------------------------------|------------------|

| Reverse biased            | Reverse biased               |                  |

| Forward biased            | Reverse biased               |                  |

| Forward biased            | Forward biased               |                  |

Uhat are the two (2) main applications of BJT?

#### https://padlet.com/nurnajahatulhuda/hba67po8p9ok 8oun

Figure below illustrate a structure of NPN transistor contain collector (C), base (B) and emitter (E). Fill in the blank.

The base (B) to emitter (E) junction is normally \_\_\_\_\_\_ biased and the resistance at the junction is \_\_\_\_\_\_.

The collector (C) to base (B) junction is normally \_\_\_\_\_\_ biased and the resistance at the junction is \_\_\_\_\_\_.

The smallest current in NPN bipolar junction transistor is the current.

**Exercise** -

#### Collector - Base Characteristic Curve Input Characteristic

□ The characteristic resembles a family of forward biased diode curves  $\Box I_B$  increases as  $V_{CE}$  decreases for a fixed value of  $V_{BE}$

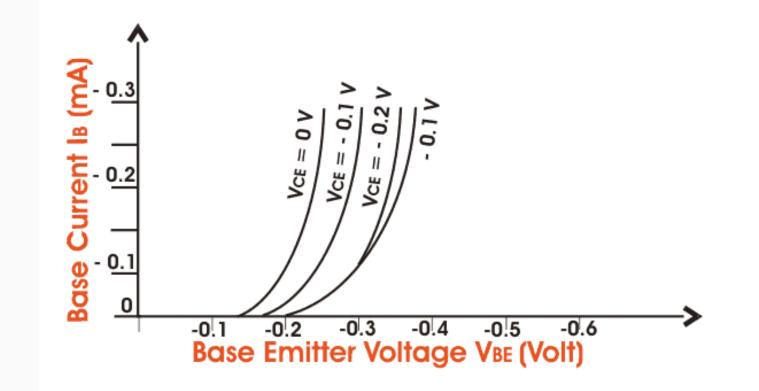

#### Collector Characteristic Curve Output Characteristic

| Active Region                                                      | Saturation Region                                                                   | Cut – Off Region                                                                                       |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| B-E junction forward biased                                        | B-E and C-E junction<br>are forward biased.                                         | B-E and C-E junction<br>are reverse biased.                                                            |

| C- B junction reverse<br>biased                                    | I <sub>B</sub> and I <sub>C</sub> are too big<br>but V <sub>CE</sub> is very small. | I <sub>B</sub> < μA but I <sub>C</sub> is not<br>zero. Avoid this<br>region for<br>undistorted signal. |

| Can be employed to<br>used as voltage and<br>current amplification | Suitable region to used as logic switch.                                            | Suitable region to used as logic switch.                                                               |

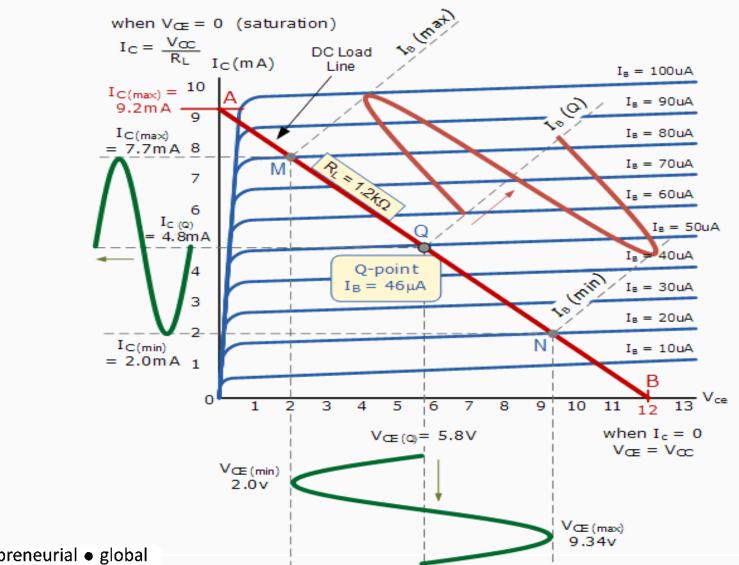

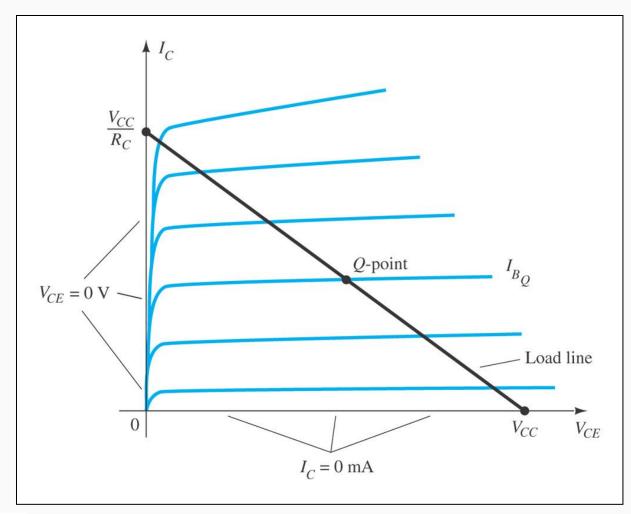

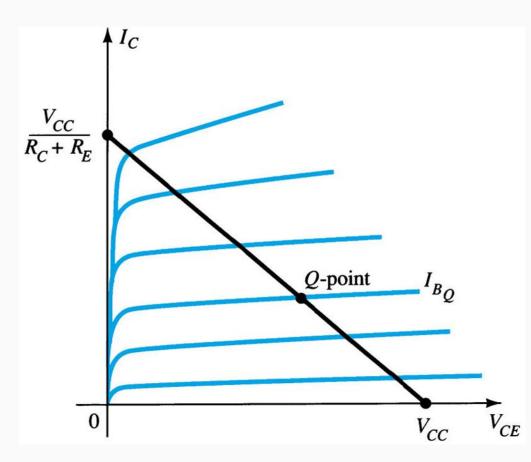

#### What is Q – Point? (DC Operating Point)

- $\Box$  When the BJT only have DC input (no ac input) it will have specific value of I<sub>c</sub> and V<sub>CE</sub>.

- □ It correspond on the specific point on the DC load line. This point is called Q point.

- $\Box$  It's a point on the collector characteristic curve ( $I_C V_{CE}$ ) with constant  $I_B$ .

# >>> Purpose of BJT Biasing

BJT should be biased to determine its operating point or Q point.

To ensure whether it is in active region to be used as amplifier or in saturation or cut-off region to be used as switch.

> A good biasing circuit must have Q – point at the center of the DC load line to obtain maximum symmetrical output swing.

21

#### **Q** – Point at the center of DC Load line

#### **Q** – Point <u>NOT</u> at the center of DC Load line

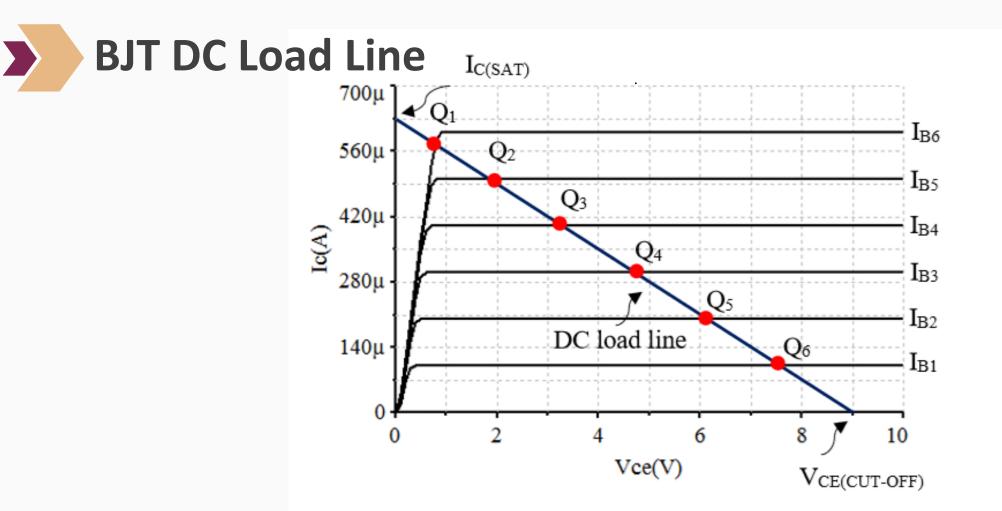

#### BJT DC Load Line

- A straight line intersecting the vertical axis at approximately I<sub>C(sat)</sub> and the horizontal axis at V<sub>CE(off)</sub>.

- I<sub>C(sat)</sub> occurs when transistor operating in saturation region

$$I_{C_{sat}} = \frac{V_{CC}}{R_C} \bigg|_{V_{CE} = 0}$$

V<sub>CE(off)</sub> occurs when transistor operating in *cut-off region*

$$V_{CE_{(off)}} = V_{CC} - I_C R_C \Big|_{I_C = 0}$$

To make sure that the chosen Q –point is useful for amplifier application, the Q-point, it is best located at the canter of the DC load line where:

$$I_{CQ} = \frac{1}{2} I_{C(SAT)}$$

and  $V_{CEQ} = \frac{1}{2} V_{CC}$

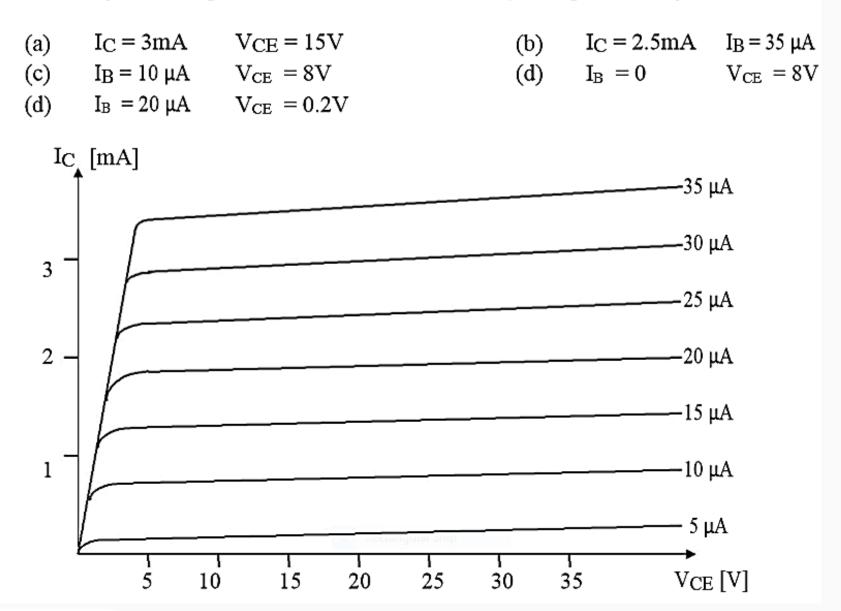

Referring to the output characteristic shown, identify the operation region if :

#### Main Types of BJT Biasing Circuit

Fixed Base Bias Circuit

Fixed Base Bias with emitter resistor

(Emitter stabilized bias circuit)

Voltage-Divider Bias Circuit

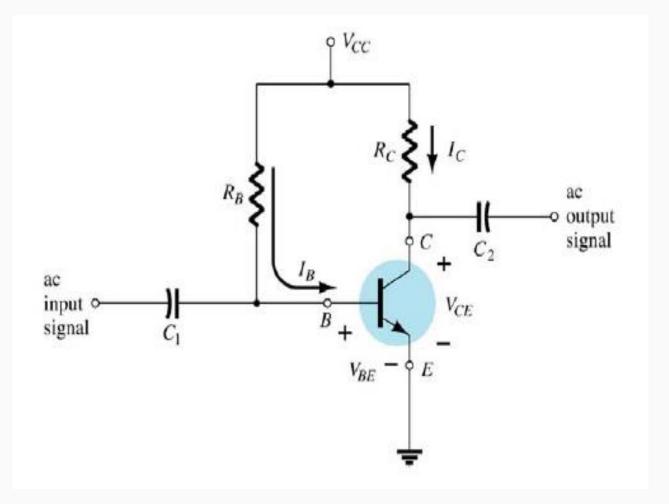

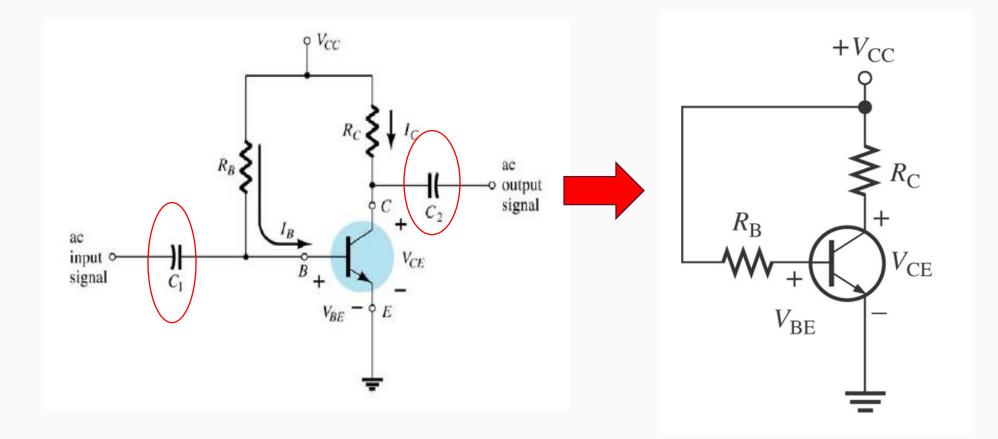

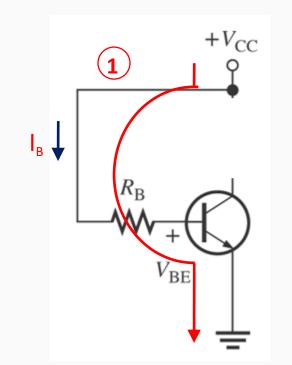

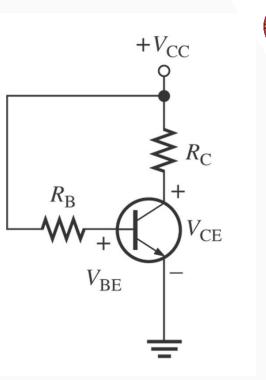

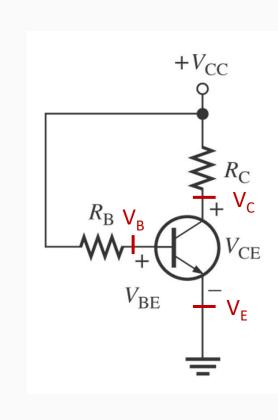

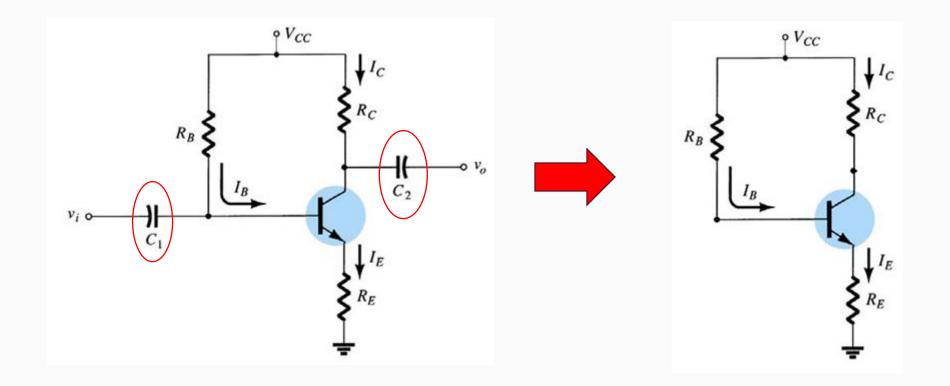

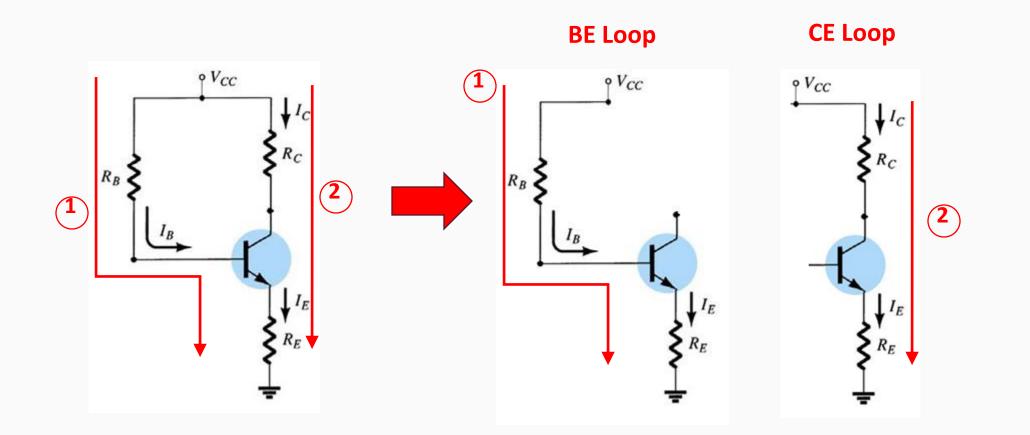

#### BJT Circuit Analysis: Fixed Bias Circuit

- This is common emitter (CE) configuration

- □ Solve the circuit using HVK

- <u>1<sup>st</sup> step</u>: Locate capacitors and replace them with an open circuit

- 2<sup>nd</sup> step: Locate 2 main loops which;

- BE loop

- CE loop

# <u>1<sup>st</sup> step</u>: Locate capacitors and replace them with an open circuit

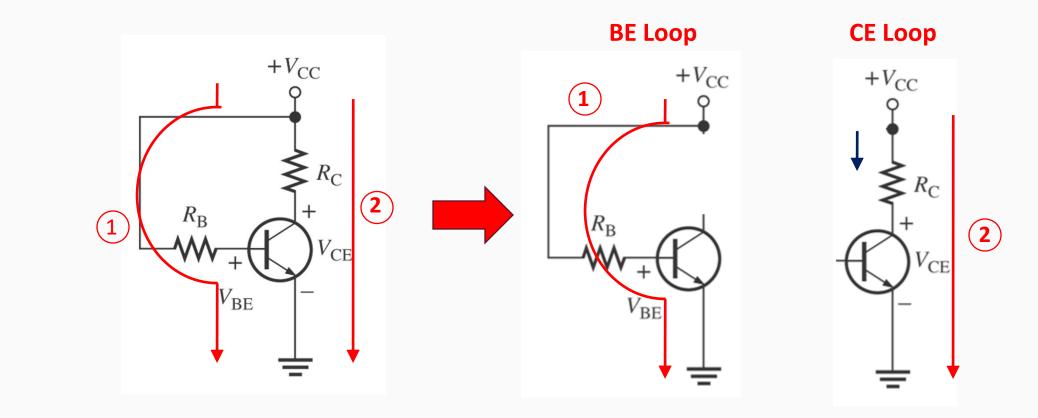

### 2<sup>nd</sup> step: Locate 2 main loops

From HVK;  $V_{CC} - I_{B}R_{B} - V_{BE} = 0$   $\therefore I_{B} = \frac{V_{CC} - V_{BE}}{R_{B}}$

31

# $+V_{CC}$ $R_C$ $+V_{CE}$ $+V_{CE}$ $+V_{CE}$

- From HVK;

- $V_{CC} I_C R_C V_{CE} = 0$  $\therefore V_{CE} = V_{CC} - I_C R_C$

- As we known;

- Substituting A with B

$$I_C = \beta I_B$$

(B)

$$I_{\rm C} = \beta_{\rm DC} \left( \frac{V_{\rm CC} - V_{\rm BE}}{R_{\rm B}} \right)$$

CE Loop Analysis

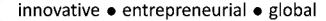

#### **BJT Circuit Analysis: Fixed Bias Circuit**

Taking the Kirchhoff voltage law (KVL) around • the B – E loop yield the following equation:

$$\mathbf{V}_{\rm CC} - \mathbf{I}_{\rm B}\mathbf{R}_{\rm B} - \mathbf{V}_{\rm BE} = \mathbf{0}$$

$$I_{B} = \frac{V_{CC} - V_{BE}}{R_{B}}$$

The collector current  $I_{C}$  is then given by

$$I_{\rm C} = \beta I_{\rm B} = \beta \left( \frac{V_{\rm CC} - V_{\rm BE}}{R_{\rm B}} \right)$$

- The voltage at the base, collector and emitter can be ٠ calculated using  $V_{\rm C} = V_{\rm CC} - I_{\rm C}R_{\rm C}$  $V_{\rm B} = V_{\rm CC} - I_{\rm B}R_{\rm B}$

- $I_{C}$  is directly dependent on  $\beta$ . This is unfavourable since  $\beta$  varies with temperature and  $I_{C}$ . • When  $I_C$  is changing, it cause  $V_{CE}$  to change. This will change the Q – point of the transistor and make the fixed base biasing circuit very unstable.

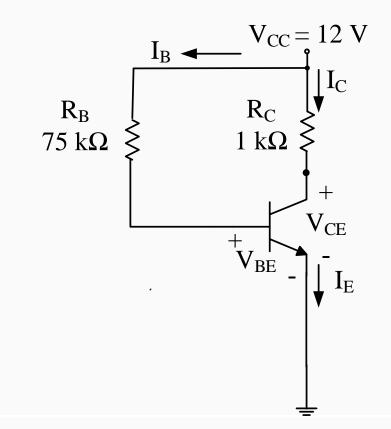

#### Example : Fixed Biasing Circuit

Draw the DC load line and find  $I_{BQ}$ ,  $I_{CQ}$ ,  $V_{CEQ}$ ,  $V_{CQ}$ ,  $V_{EQ}$  and  $V_{BQ}$ . Comment on the location of the Q – point.

> $V_{CC} = 8 V$  $I_{B} \blacktriangleleft$  $R_{\rm C}$ R<sub>B</sub>  $2 k\Omega$  $360 \text{ k}\Omega$ V<sub>CE</sub> +V<sub>BE</sub>  $I_{C}(mA)$ 4 Q - point 2  $V_{CE}(V)$ 3.94 8

Using C - E Loop:

$$V_{CC} - I_B R_B - V_{BE} = 0$$

$I_B = I_{BQ} = \frac{V_{CC} - V_{BE}}{R_B} = \frac{8 - 0.7}{360k} = \frac{20.28 \ \mu A}{20.28 \ \mu A}$

$I_C = I_{CQ} = \beta I_B = (100) 20.28 \ \mu = \frac{2.03 \ m A}{20.28}$

Using C - E Loop:

$V_{CC} - I_C R_C - V_{CE} = 0$  .....(A)

$V_{CE} = V_{CEQ} = V_{CC} - I_{CQ} R_C = 8 - (2.03 \ m \times 2k) = 3.94 \ V$

when  $I_C = 0$ ,  $V_{CE} = V_{CE(CUT-OFF)} = V_{CC} = 8V$

when  $V_{CE} = 0$ ,  $I_C = I_{C(SAT)} = \frac{V_{CC}}{R_C + R_E} = \frac{8}{2k} = 4 \ mA$

\*\* The Q – point is in the active region. Therefore this biasing circuit is suitable to be used in amplifier.

innovative • entrepreneurial • global

#### Example : Fixed Bias Circuit

$V_{CC} = +12 \text{ V}$  $R_B$  $I_C$  $240 k\Omega$ ac output  $10 \, \mu F$  $C_1$ ac V<sub>CE</sub>  $\beta = 50$ input 10 µF

Find  $I_C$ ,  $I_B$ ,  $V_{CE}$ ,  $V_B$ ,  $V_C$ ,  $V_{BC}$ ? (Silicon transistor) Construct the DC load line then determine the operation region of the Q – point.

Answers;

- IC = 2.35 mA

- IB = 47.08 μA

- VCE = 6.83V

- VB = 0.7V

- VC = 6.83V

- VBC = -6.13V

step 1: open all capacitors and redraw the circuit. step 2 : B - E Loop KVL  $12 - I_{\rm R}R_{\rm R} - V_{\rm RE} = 0$  $I_{\rm B} = \frac{12 - V_{\rm BE}}{R_{\rm B}} = \frac{12 - 0.7}{240k} = \frac{47.1\,\mu\rm{A}}{\sqrt{2}}$ using relation  $I_E = (1 + \beta)I_B$  and  $I_E \approx I_C$  $I_E \approx I_C = (1+50) \times 47.1 \,\mu = 2.40 \,\text{mA}$ step 3 C-ELoop KVL

$\frac{1}{C - E \text{ Loop KVL} }$   $12 - I_C R_C - V_{CE} = 0$   $V_{CE} = 12 - I_C R_C = 12 - (2.40 \text{ m} \times 2.2 \text{k}) = 6.72 \text{V}$

From the circuit,  $V_E = 0V$ . it is known that  $V_{BE} = 0.7V$  $V_{\rm BE} = V_{\rm B} - V_{\rm E}$  $\therefore V_{\rm B} = V_{\rm BF} = 0.7 \, \rm V$ at the collector (C) terminal:  $V_{ce} = V_c - V_e$  and  $V_e = 0V$  $\therefore V_{\rm C} = V_{\rm CF} = 6.72 \, {\rm V}$ at the base (B) terminal :  $V_{\rm RC} = V_{\rm R} - V_{\rm C}$  $V_{\rm RC} = V_{\rm R} - V_{\rm C} = 0.7 - 6.72 = -6.02 \,\rm V$

$\sqrt{}$

# **Exercise : Fixed Bias Circuit**

For the biasing circuit shown, determine the Q – point ( $I_{CQ}$ ,  $V_{CEQ}$ ) and confirm its operation region. Construct the DC load line and evaluate the location of the Q – point. Given  $\beta$  = 100. Redo if  $\beta$  is changed to 129.

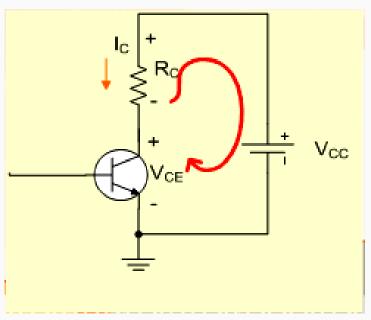

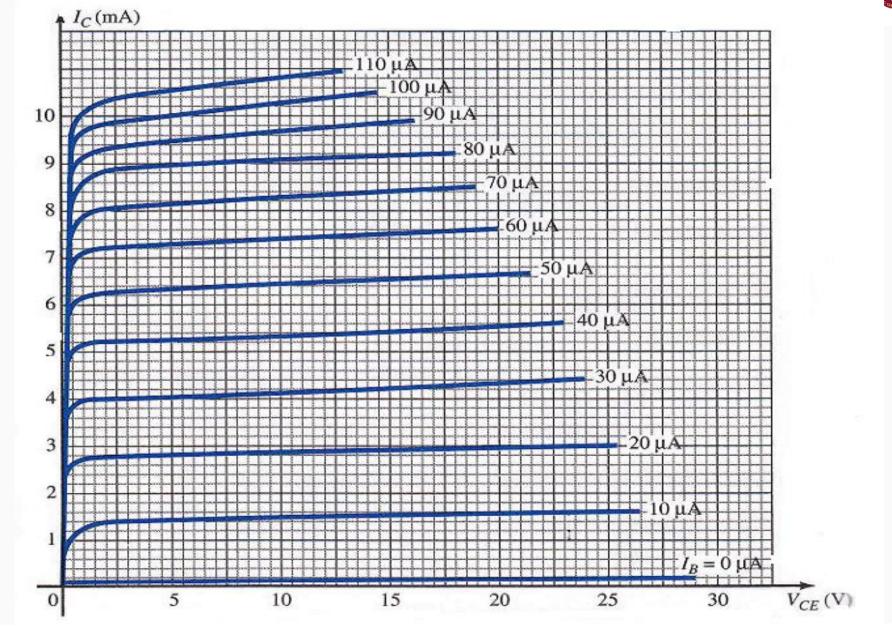

# Load Line Analysis – Fixed Bias Circuit

- We investigate how the actual Q-point is determined.

- Referring to the figure below (output loop), a straight line can be drawn at the output characteristics curve. This line is called the load line.

- This line connects each separate Q-point.

- At any point along the load line, values of  $I_B$ ,  $I_C$  and  $V_{CE}$  can be picked from the graph.

- The process to plot the load line are as follows:

# Load Line Analysis – Fixed Bias Circuit

### • Step 1:

Apply KVL at output loop,  $V_{CE} = V_{CC} - I_C R_C$  (1) Choose  $I_C = 0$  mA. Substitute into (1), we get  $V_{CE} = V_{CC}$  (2)  $\rightarrow$  intersects the x-axis

#### • Step 2:

Choose  $V_{CE}$  = 0V and substitute into (1), we get  $I_C = V_{CC}/R_C$  (3)  $\rightarrow$  intersects the y-axis

### • Step 3:

Joining these two points defined by step (2) & (3), we get a straight line that can be drawn as in the next figure.

# Load Line Analysis – Fixed Bias Circuit

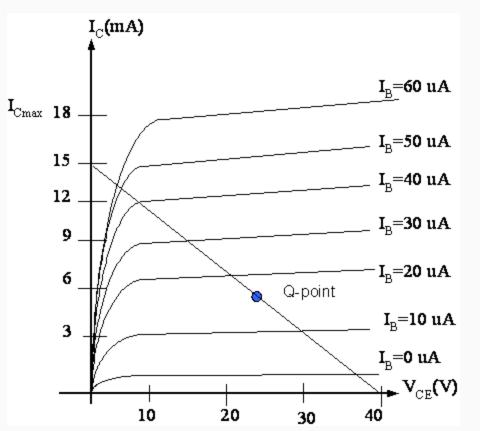

Given the load line in the figure below, define the Q-point & determine the required values of  $V_{CC}$ ,  $R_C$  and  $R_B$  for a fixed bias configuration. (Given  $I_{BQ}$  at 17  $\mu$ A)

$$V_{CC} = 40 \text{ V}$$

$$I_{C} = \frac{V_{CC}}{R_{C}}$$

$$R_{C} = 2.67 \text{ k}\Omega$$

at Q - point;  $I_B = 17 \mu A$  $R_B = \underline{2311 \, k\Omega}$

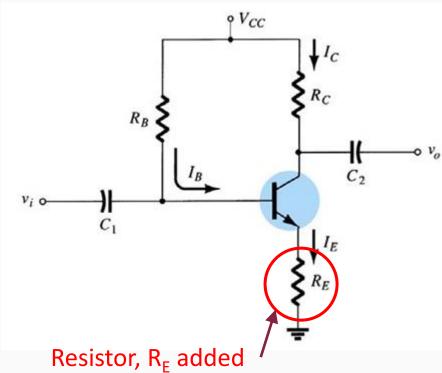

# Disadvantages of Fixed Biasing

- Unstable because it is too dependent on β and produce change of Qpoint

- General For improved bias stability , add emitter resistor to dc bias.

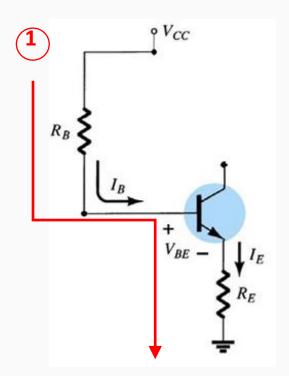

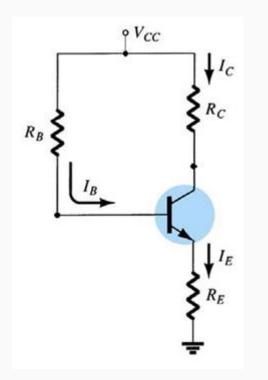

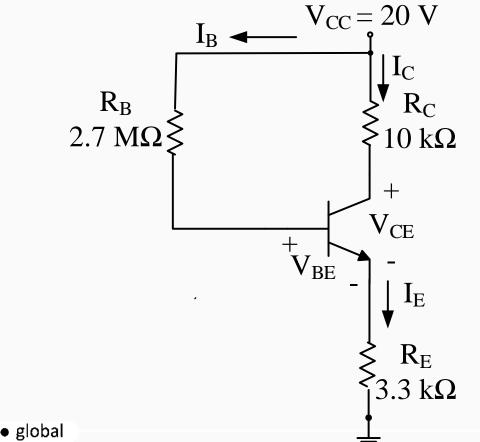

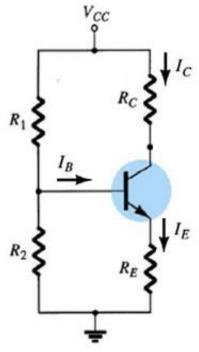

# Fixed Bias with emitter resistor (Emitter Stabilized Bias)

- •An emitter resistor,  $R_E$  is added to improve stability

- Solve the circuit using HVK

- <u>1<sup>st</sup> step</u>: Locate capacitors and replace them with an open circuit

- <u>2<sup>nd</sup> step</u>: Locate 2 main loops which;

➢ BE loop

➢ CE loop

# <u>1<sup>st</sup> step</u>: Locate capacitors and replace them with an open circuit

# 2<sup>nd</sup> step: Locate 2 main loops

Fixed Base Bias with Emitter Resister

From HVK;

$V_{CC} - I_B R_B - V_{BE} - I_E R_E = 0$ Recall;  $I_E = (\beta + 1)I_B$

Substitute for IE

$$V_{CC} - I_B R_B - V_{BE} - (\beta + 1) I_B R_E = 0$$

$$\therefore I_B = \frac{V_{CC} - V_{BE}}{R_B + (\beta + 1) R_E}$$

$\begin{array}{c} \bullet V_{CC} \\ & \downarrow I_{C} \\ & R_{C} \\ & \downarrow I_{E} \\ & \downarrow I_{E} \\ & R_{E} \end{array}$

From HVK;  $V_{CC} - I_C R_C - V_{CE} - I_E R_E = 0$ Assume;  $I_E \approx I_C$ Therefore;  $\therefore V_{CE} = V_{CC} - I_C (R_C + R_E)$

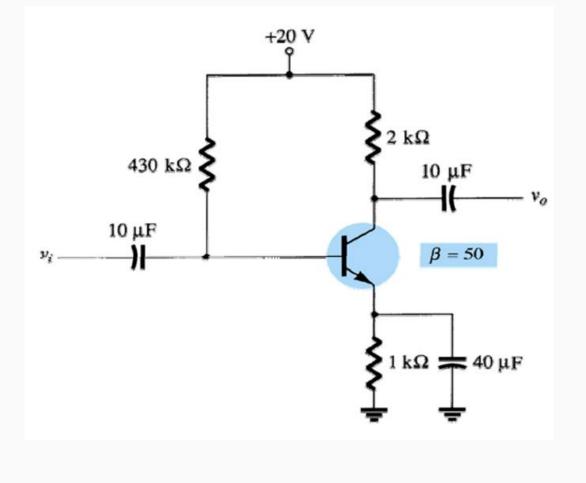

# Example Emitter Stabilized Bias

innovative • entrepreneurial • global

Find I<sub>CQ</sub>, I<sub>BQ</sub>, V<sub>CEQ</sub>, V<sub>BQ</sub>, V<sub>CQ</sub>, V<sub>EQ</sub> & V<sub>BCQ</sub>? (Silicon transistor);

### Answers;

- l<sub>cq</sub> = 2.01 mA

- $I_{BQ} = 40.1 \ \mu A$

$$V_{BQ} = 2.71V$$

$$V_{EQ} = 2.01V$$

$$V_{BCO} = -13.27V$$

step 1: open all capacitors and redraw the circuit.

step 2: B - E Loop KVL  $20 - I_R R_R - V_{RF} - I_F R_F = 0$ using relation  $I_{\rm F} = (1 + \beta) I_{\rm B}$  $20 - I_{\rm B}R_{\rm B} - V_{\rm BF} - R_{\rm F}(1+\beta)I_{\rm B} = 0$ V  $I_{\rm B} = \frac{20 - V_{\rm BE}}{R_{\rm P} + R_{\rm E}(1+\beta)} = \frac{20 - 0.7}{430k + 1k(1+50)} = \frac{40.1\,\mu\text{A}}{430k + 1k(1+50)}$ using relation  $I_E = (1+\beta)I_B$  and  $I_E \approx I_C$  $I_{\rm F} \approx I_{\rm C} = (1+50) \times 40.1 \,\mu = 2.05 \,\mathrm{mA}$ step 3 C-E Loop KVL  $20 - I_C R_C - I_E R_E V_{CE} = 0$  $V_{CE} = 20 - I_C R_C - I_E R_E$  $= 20 - (2.05 \text{ m} \times 2\text{k}) - (2.05 \text{ m} \times 1\text{k}) = 13.85\text{V}$

### it is known that $V_{RF} = 0.7V$ $V_{\rm RF} = V_{\rm R} - V_{\rm F}$ and $V_{\rm F} = I_{\rm F}R_{\rm F}$ and $\therefore V_{\rm E} = I_{\rm E}R_{\rm E} = 2.05 \,{\rm m} \times 1k = 2.05 \,{\rm V}$ $\therefore V_{\rm R} = V_{\rm RF} + V_{\rm F} = 0.7 + 2.05 = 2.75 \, \text{V}$ $V_{CE} = V_C - V_E$ from $\therefore V_{C} = V_{CE} + V_{E} = 13.85 + 2.05 = 15.9 \text{ V}$ $V_{BC} = V_{R} - V_{C} = 2.75 - 15.9 = -13.15V$ this BJT is biased in FORWARD ACTIVE

# Load Line Analysis – Emitter (Stabilized Bias) Circuit

- For  $V_{CE} = 0$ , the transistor will be in saturation region

- Taking the transistor's saturation equation:  $I_{C_{sat}} = \frac{V_{CC}}{R_C + R_E}$

• For

$$I_C = 0$$

:  $I_C \approx I_E$

$I_C = \frac{V_{CC} - V_{CE}}{R_C + R_E} = 0$

$\therefore V_{CE} = V_{CC}$

So, the load-line becomes:

Find  $I_{CQ}$ ,  $I_{BQ}$ ,  $V_{CEQ}$ ,  $V_{BQ}$ ,  $V_{CQ}$ ,  $V_{EQ}$  &  $V_{BCQ}$ ? (Silicon transistor). Construct the DC load line and determine the transistor operation region

innovative • entrepreneurial • global

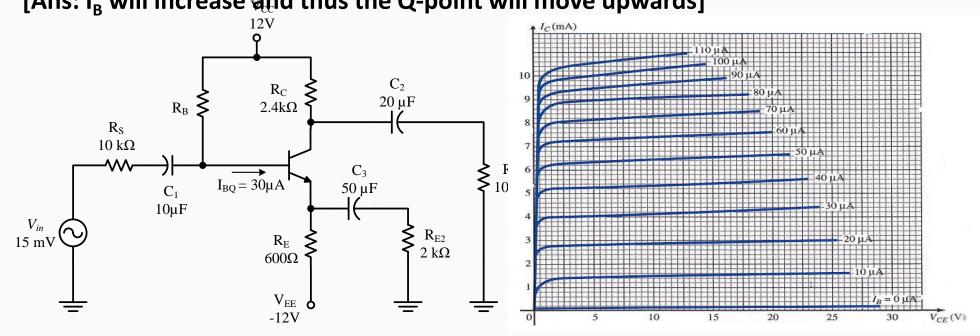

# Exercise Test 2 2013/2014/2

A BJT amplifier circuit in Figure Q2(a) has the following specifications:  $I_{BQ} = 30\mu A$  and  $V_{BE} = 0.7V$ .

- (i) Determine Q-point (I<sub>CQ</sub>, V<sub>CEQ</sub>) of the circuit using the output characteristic graph in Figure Q2(b)

[Ans: I<sub>CQ</sub> = 4.2mA : V<sub>CEQ</sub> = 11.5V]

- (ii) Calculate  $\beta$  at the Q-point [Ans:  $\beta$ =140]

- (iii) Calculate  $R_B$  [Ans: 692k $\Omega$ ]

- (iv) What is the effect on the Q-point of the circuit, when R<sub>B</sub> is decreased?

[Ans: I<sub>B</sub> will increase and thus the Q-point will move upwards]

Μ

UNIVERSITI TEKNOLOGI MALAYSIA

# **Exercise**

Determine  $I_{BQ}$ ,  $I_{CQ}$ ,  $V_{CEQ}$ ,  $V_B$ ,  $V_C$ ,  $V_E$ . Given  $\beta$ = hFE= 100 and  $V_{BE}$ = 0.7V. Sketch the DC load line of the circuit. [Ans:  $I_{BQ}$  =29.18uA,  $I_{CQ}$  =2.92 mA,  $V_{CEQ}$ =8.61V,  $V_B$ =5.12V,  $V_C$ =12.99V,  $V_E$  = 4.38V]

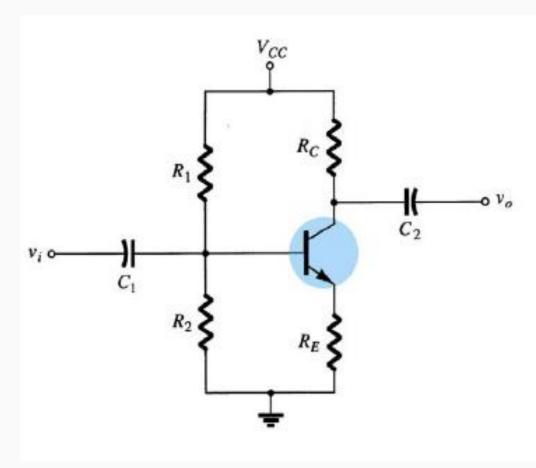

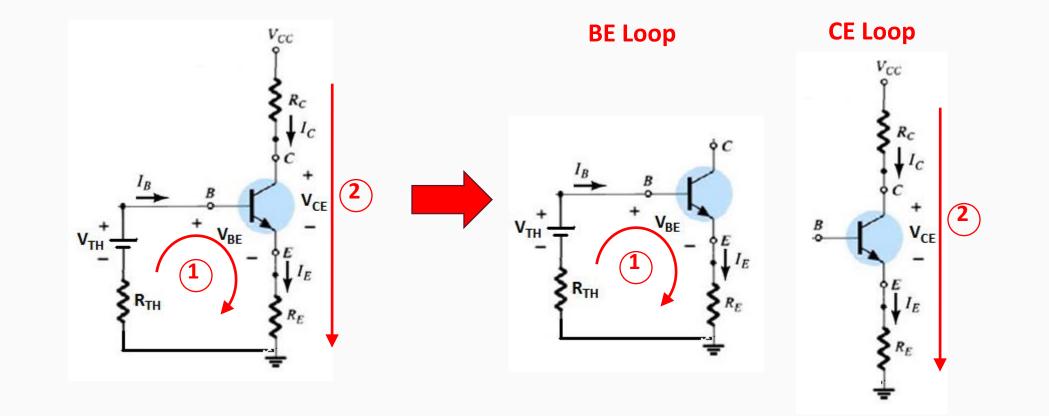

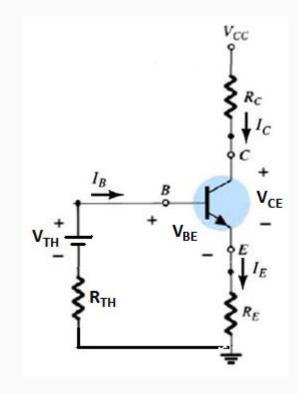

# Voltage Divider Bias Circuit

Provides good Q-point stability with a single polarity supply voltage

□Solve the circuit using HVK

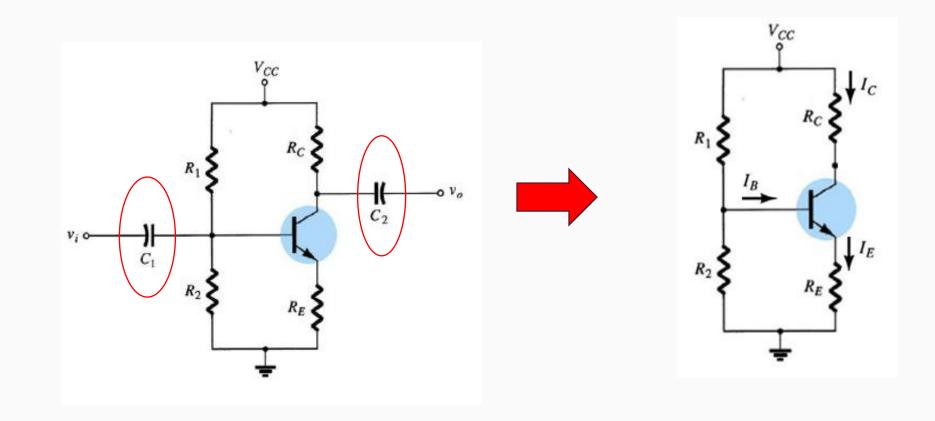

□ <u>1<sup>st</sup> step</u>: Locate capacitors and replace them with an open circuit

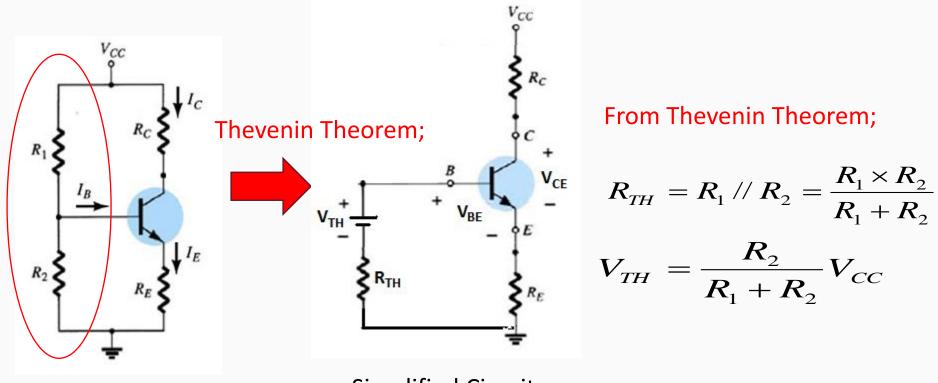

2<sup>nd</sup> step: Simplified circuit using Thevenin Theorem

□<u>3<sup>rd</sup> step</u>: Locate 2 main loops which;

BE loop

CE loop

# Voltage Divider Bias Approximation Analysis

For approximation analysis we can assume

$V_{TH} = V_B$ but the following condition must satisfy:

$\beta R_E \ge 10R_2$

### <u>1<sup>st</sup> step</u>: Locate capacitors and replace them with an open circuit

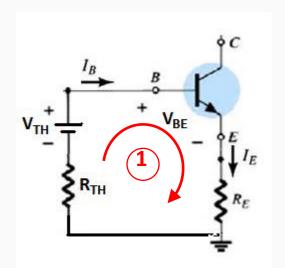

# <u>2<sup>nd</sup> step</u>: : Simplified circuit using Thevenin Theorem<sup>®</sup>

Voltage Divider Bias Circuit

Simplified Circuit

From HVK;

$$V_{TH} - I_B R_{TH} - V_{BE} - I_E R_E = 0$$

Recall;  $I_E = (\beta + 1)I_B$

Subtitute for IE

$$V_{TH} - I_B R_{TH} - V_{BE} - (\beta + 1) I_B R_E = 0$$

$$\therefore I_B = \frac{V_{TH} - V_{BE}}{R_{RTH} + (\beta + 1) R_E}$$

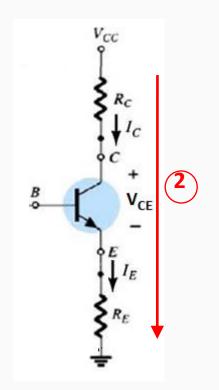

# **CE Loop Analysis**

Voltage Divider Bias Circuit

From HVK;  $V_{CC} - I_C R_C - V_{CE} - I_E R_E = 0$ Assume;  $I_E \approx I_C$ Therefore;  $\therefore V_{CE} = V_{CC} - I_C (R_C + R_E)$

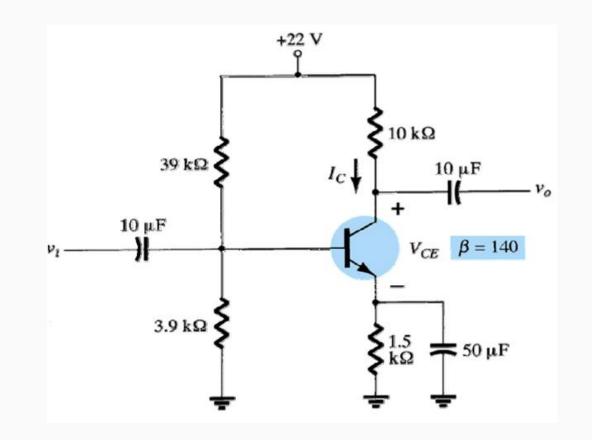

# Example Voltage Divider Bias Circuit: Single Supply

Find R<sub>TH</sub>, V<sub>TH</sub>, I<sub>CQ</sub>, I<sub>BQ</sub>, V<sub>CEQ</sub>, V<sub>BQ</sub>, V<sub>CQ</sub>, V<sub>EQ</sub> & V<sub>BCQ</sub>? (Silicon transistor). Construct the DC load line

Answers; RTH =  $3.55 \text{ k}\Omega$ VTH = 2VICQ = 0.85 mA $IBQ = 6.05 \ \mu A$ VCEQ = 12.9VVBQ = 1.978VVEQ = 1.275V

VCQ = 13.5V

step 1: open all capacitors and redraw the circuit.

step 2 : calculate  $V_{th}$  and  $R_{th}$

$$V_{th} = \frac{3.9k}{3.9k + 39k} \times 22 = 2V$$

$$R_{th} = \frac{3.9k \times 39k}{3.9k + 39k} = 3.55 \text{ k}\Omega$$

then redraw the circuit.

step 3:

$$B - E \text{ Loop KVL}$$

$$V_{TH} - I_B R_{TH} - V_{BE} - I_E R_E = 0$$

$$2 - I_B (3.55 \text{ k}) - 0.7 - I_E (1.5 \text{ k}) = 0$$

using relation  $I_E = (1 + \beta) I_B$

$$2 - I_B (3.55 \text{ k}) - 0.7 - I_B (1 + \beta) (1.5 \text{ k}) = 0$$

$$I_B = \frac{2 - 0.7}{3.55 \text{ k} + 1.5 \text{ k} (1 + 140)} = \frac{6.05 \,\mu\text{A}}{1}$$

using relation  $I_E = (1 + \beta) I_B$  and  $I_E \approx I_C$

innovative • entrepreneurial • global  $I_E \approx I_C = (1 + 140) \times 6.05 \,\mu = 0.85 \,\text{mA}$

C - E Loop KVL

$$V_{CC} - I_C R_C - V_{CE} - I_E R_E = 0$$

assume  $I_C \approx I_E$

$V_{CE} = V_{CC} - I_C R_C - I_E R_E = 22 - 10k(0.85m) - 1.5k(0.85m)$

$V_{CE} = \underline{12.19V}$

it is known that  $V_{BE} = 0.7V$

and  $V_{BE} = V_B - V_E$  and  $V_E = I_E R_E$

$\therefore V_E = I_E R_E = 0.85m \times 1.5k = \underline{1.28 V}$

$\therefore V_B = V_{BE} + V_E = 0.7 + 1.28 = \underline{1.98 V} \approx V_{TH}$

from  $V_{CE} = V_C - V_E$

$\therefore V_C = V_{CE} + V_E = 12.19 + 1.28 = \underline{13.51 V}$

$V_{BC} = V_B - V_C = 0.7 - 13.51 = -\underline{12.81V}$

this BJT is biased in FORWARD ACTIVE

innovative • entrepreneurial • global

## Example Voltage Divider Bias with 2 supply

Determine  $I_{BQ}$ ,  $I_{CQ}$ ,  $V_{CEQ}$ ,  $V_{BQ}$ ,  $V_{CQ}$ ,  $V_{EQ}$ . Given  $\beta = h_{FE} = 120$  and  $V_{BF} = 0.7V$ . [Ans:  $I_{BQ} = 35.35 \mu A$ ,  $I_{CQ} = 4.24 m A$ ,  $V_{CEQ} = 20.92 V$ ,  $V_{BO} = -11.6 V$ ,  $V_{co}$ =8.55V,  $V_{EO}$ =-12.37V]  $QV_{CC} = +20 V$ 10 µF  $C_1$  $\beta = 120$ ViO  $10 \mu F$  $\oint V_{EE} = -20 \text{ V}$

$\underline{\underline{step 1}}: open all capacitors and draw the DC equivalent circuit$

$\underline{step \ 2}$  : calculate  $V_{th}$  and R  $_{th}$

$$\begin{split} V_{th} &= \frac{R_2}{R_1 + R_2} \times (+V_{CC}) + \frac{R_1}{R_1 + R_2} \times (-V_{CC}) \\ V_{th} &= \frac{2.2k}{2.2k + 8.2k} \times (+20) + \frac{8.2k}{2.2k + 8.2k} \times (-20) = -11.54V \\ R_{th} &= \frac{2.2k \times 8.2k}{2.2k + 8.2k} = 1.73k\Omega \\ \hline R_{th} &= \frac{2.2k \times 8.2k}{2.2k + 8.2k} = 1.73k\Omega \\ \hline step 3: \\ \hline B - E \text{ Loop KVL} \\ V_{TH} - I_B R_{TH} - V_{BE} - I_E R_E + V_{EE} = 0 \\ \text{using relation} \quad I_E = (1 + \beta) I_B \\ V_{TH} - I_B R_{TH} - V_{BE} - (1 + \beta) I_B R_E + V_{EE} = 0 \\ -11.54 - I_B (1.73k) - 0.7 - (1 + 120) I_B (1.8k) + 20 = 0 \\ I_B = I_{BQ} = \frac{20 - 11.54 - 0.7}{1.73k + 1.8k(1 + 120)} = \frac{35.35 \,\mu\text{A}}{1.73k + 1.8k(1 + 120)} \\ \text{using relation} \quad I_E = (1 + \beta) I_B \text{ and } I_E \approx I_C \\ I_E \approx I_C \approx I_{CQ} = (1 + 120) \times 35.35 \,\mu = \frac{4.28 \,\text{mA}}{1.28 \,\text{mA}} \end{split}$$

C - E Loop KVL

$$V_{CC} - I_C R_C - V_{CE} - I_E R_E + V_{EE} = 0$$

assume  $I_C \approx I_E$

$V_{CE} = V_{CC} - I_C R_C - I_E R_E + V_{EE} = 20 - 2.7k(4.28m) - 1.8k(4.28m) + 20$

$V_{CE} = \underline{V_{CEQ}} = 20.74V$

It is known that  $V_{BE} = 0.7V$

and  $V_{BE} = V_B - V_E$  and  $V_E = I_E R_E - V_{EE}$

$\therefore V_E = I_E R_E - V_{EE} = 1.8k(4.28m) - 20 = -12.3 V$

$\therefore V_B = V_{BE} + V_E = 0.7 - 12.3 = -11.6V \approx V_{TH}$

from  $V_{CE} = V_C - V_E$

$\therefore V_C = V_{CE} + V_E = 20.74 - 12.3 = 8.44 V$

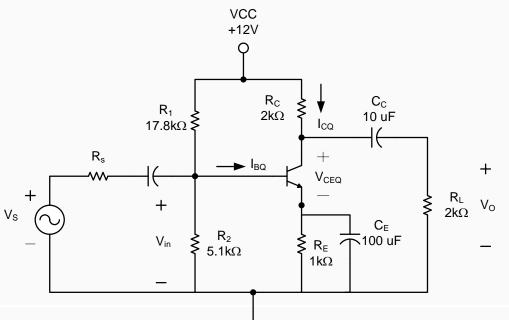

# Exercise FINAL SEU 2012 2010/2011/2

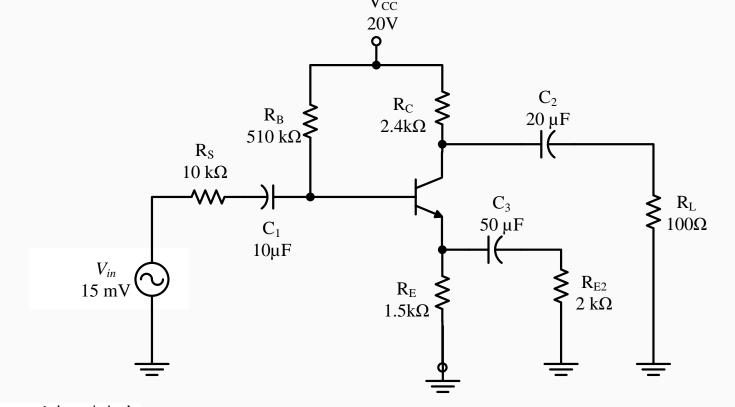

Refer to a small signal amplifier circuit in Figure Q3. The transistor's parameter are:

$\beta_{\text{DC}} = \beta_{\text{AC}} = 100$ ,  $V_{\text{BE}} = 0.7$ V,  $V_{\text{T}} = 26$ mV

- I. Draw the DC equivalent circuit.

- II. Calculate the base and collector current,  $I_{BQ}$  and  $I_{CQ}$ . [Ans:  $I_{BQ}$ =18.7µA,  $I_{CQ}$ =1.87mA]

- III. Calculate the collector to emitter voltage, V<sub>CEQ</sub>. [Ans=V<sub>CE</sub>=6.3V]

- IV. Calculate new Q-point ( $I_{BQ}$  and  $I_{CQ}$ ) if  $R_2$  is halved [Ans:  $I_B=7.7\mu A$ ,  $I_C=0.77mA$ ]

÷

## Load Line Analysis - Voltage Divider Bias

□For the load-line analysis, the cutoff region still results the same as the fixed bias and emitter bias configuration:

$$V_{CE} = V_{CC} \Big|_{I_C = 0}$$

And for the saturation region:

$$I_{C_{sat}} = \frac{V_{CC}}{R_C + R_E} \bigg|_{CE} = 0$$

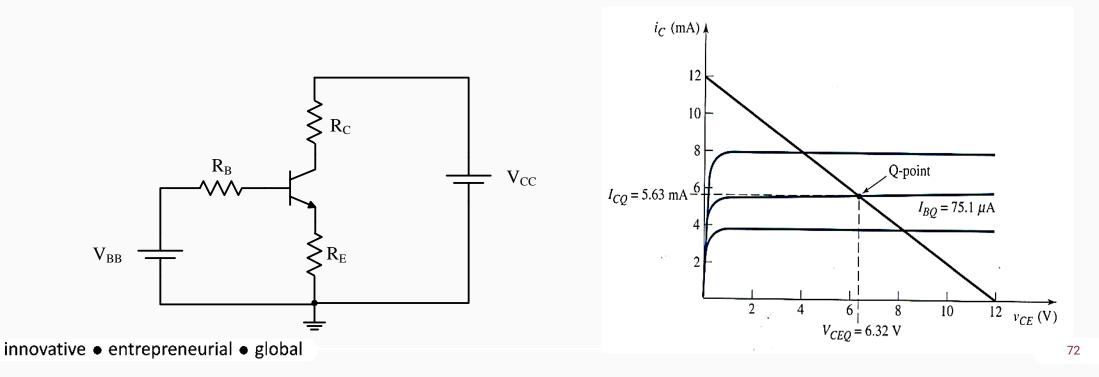

# Exercise Final Exam 2013/2014/2

The dc load line of the circuit and the characteristic is as shown. Based on the figures,

- (i) Determine the common emitter current gain,  $\beta$ , and the emitter current,  $I_E$ . [Ans:  $\beta$  = 75,  $I_E$  = 5.71mA]

- (ii) Determine  $R_B$  and  $R_C$  such that the circuit yields the given Q-point. Given  $V_{BE} = 0.7 \text{ V}$ ,  $V_{BB} = 6 \text{ V}$ , and  $R_E = 600 \Omega$ . [Ans:  $R_B = 25k\Omega$ ,  $R_C = 400\Omega$ ]

## **DC Biasing Circuit for PNP BJT**

- □All the previous analysis and technique used in NPN BJT can be applied to PNP BJT.

- This is because the amount of current is the same;  $I_E = I_B + I_C$

- □ The major different is the direction of current flowing.

- PNP BJT current flow from emitter to collector.

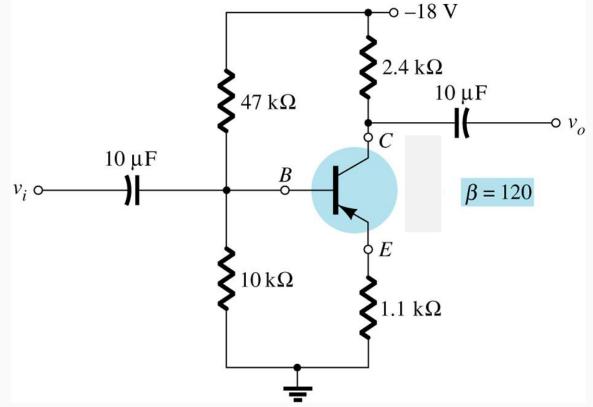

### Example Voltage Divider PNP

Determine  $I_{BQ}$ ,  $I_{CQ}$ ,  $V_{CEQ}$ ,  $V_{B}$ ,  $V_{C}$  and  $V_{E}$ . Given  $\beta = 120$  and  $V_{EB} = 0.7$ . [Ans:  $I_{BQ} = 17.4$ uA,  $I_{CQ} = 2.09$  mA,  $V_{CEQ} = -10.68$ ,  $V_{B} = -3V$ ,  $V_{C} = -12.98V$  and  $V_{E} = -2.32V$ ]

$R_{\rm C} \stackrel{\rm V_{\rm CC}}{\underset{\rm 2.4 \ k\Omega}{\overset{\rm V_{\rm C}}{\overset{\rm V_{\rm CC}}{\overset{\rm (-18 \ V)}{\overset{\rm (-18 \ V)}}{$

R<sub>E</sub> 1.1 kΩ

$\underline{\underline{step 1}}$ : open all capacitors and draw the DC equivalent circuit.

step 2 : calculate  $V_{th}$  and  $R_{th}$  $V_{th} = \frac{10k}{10k + 47k} \times -18 = -3.16V$  $R_{th} = \frac{10k \times 47k}{10k + 47k} = 8.25 \text{ k}\Omega$ R<sub>Th</sub>  $8.25 \text{ k}\Omega \text{ B}$ then redraw the circuit. - 3.16 V  $\underline{\text{step 3}}$ : E - B Loop KVL  $I_E R_E - V_{EB} V_{TH} - I_B R_{TH} + V_{TH} = 0$ using relation  $I_{\rm F} = (1+\beta)I_{\rm B}$  $I_{B}(1+\beta)R_{E} - V_{EB} - I_{B}R_{TH} + V_{TH} = 0$  $I_{\rm B}(1+120)(1.1k) - 0.7 - I_{\rm B}(8.25 k) + 3.16 = 0$ using relation  $I_{E} = (1 + \beta)I_{B}$  and  $I_{E} \approx I_{C}$  $I_{E} \approx I_{C} \approx I_{CO} = (1+120) \times 17.4 \,\mu = 2.09 \,\text{mA}$

innovative • entrepreneurial • global

Solution

### E-CLoopKVL $-I_{E}R_{E} - V_{EC} - I_{C}R_{C} + V_{CC} = 0$ assume $I_C \approx I_F$ $V_{\rm FC} = I_{\rm F}R_{\rm F} - I_{\rm C}R_{\rm C} + V_{\rm CC} = -1.1k(2.09m) - 2.4k(2.09m) + 18$ $V_{EC} = V_{ECO} = 10.69V$ $\therefore V_{CE} = V_{CEO} = -10.69V$ it is known that $V_{FR} = 0.7V$ $V_{\rm FB} = V_{\rm F} - V_{\rm B}$ and $V_{\rm F} = -I_{\rm F}R_{\rm F}$ and $\therefore V_{\rm E} = -I_{\rm E}R_{\rm E} = -2.09 \,{\rm m} \times 1.1 \,{\rm k} = -2.3 \,{\rm V}$ $\therefore V_{\rm B} = V_{\rm F} - V_{\rm FB} = -2.3 - 0.7 = -3 \, \text{V}$ from $V_{EC} = V_{E} - V_{C}$ $\therefore V_{\rm C} = V_{\rm E} - V_{\rm EC} = -2.3 - 10.69 = -12.99 \, \text{V}$

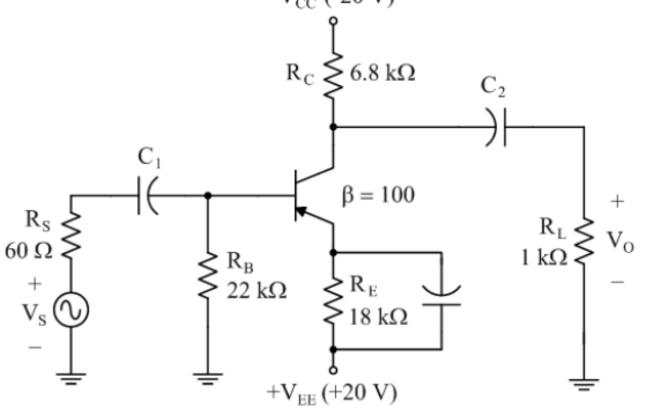

### Example Fixed Bias with 2 supply

Determine  $I_{BQ}$ ,  $I_{CQ}$ ,  $V_{CEQ}$ ,  $V_B$ ,  $V_C$ ,  $V_E$ . Given  $\beta = h_{FE} = 100$  and  $V_{EB} = 0.7V$ . [Ans:  $I_{BQ} = 10.49$ uA,  $I_{CQ} = 1.05$ mA,  $V_{CEQ} = -13.96$ V,  $V_B = 0.2$ V  $V_C = -12.86$ V and  $V_E = 0.93$ V]  $-V_{cc}$  (-20 V)

# Solution

$\underline{\underline{step 1}}: \text{ open all capacitors and draw the DC equivalent circuit.}$  $\underline{\underline{step 2}}:$

E - B Loop KVL  $20 - I_E R_E - V_{EB} - I_B R_B = 0$ using relation  $I_E = (1+\beta) I_B$   $20 - (1+\beta) I_B R_E - V_{EB} - I_B R_B = 0$  $I_B = \frac{20 - V_{EB}}{R_B + R_E (1+\beta)} = \frac{20 - 0.7}{22k + 18k(1+100)} = \frac{10.49 \,\mu A}{22k + 18k(1+100)}$

using relation  $I_E \approx I_C$  $I_E \approx I_C = (1+100) \times 10.49 \,\mu = \underline{1.06 \,\text{mA}}$

$$\frac{\text{step 3}}{\text{E} - \text{C Loop KVL}}$$

$$V_{\text{EE}} - I_{\text{E}}R_{\text{E}} - V_{\text{EC}} - I_{\text{C}}R_{\text{C}} + V_{\text{CC}} = 0$$

$$20 - 18k(1.06) - V_{\text{EC}} - 6.8k(1.06) + 20 = 0$$

$$V_{\text{EC}} = 20 - 18k(1.06) - 6.8k(1.06) + 20$$

$$V_{\text{EC}} = V_{\text{ECQ}} = \underline{13.73V}$$

$$\therefore V_{\text{CE}} = V_{\text{CEQ}} = \underline{-13.73V}$$

We know  $\Rightarrow V_{\text{EB}} = V_{\text{E}} - V_{\text{B}}$  and  $V_{\text{E}} = -I_{\text{E}}R_{\text{E}} + V_{\text{EE}}$

Therefore

$$V_{\text{E}} = -I_{\text{E}}R_{\text{E}} + V_{\text{EE}} = (-1.06m)18k + 20 = \underline{0.92V}$$

$$\therefore V_{\text{B}} = V_{\text{E}} - V_{\text{EB}} = 0.92 - 0.7 = \underline{0.22V}$$

and  $V_{\text{C}} = V_{\text{E}} - V_{\text{EC}} = 0.92 - 13.73 = \underline{-12.81V}$

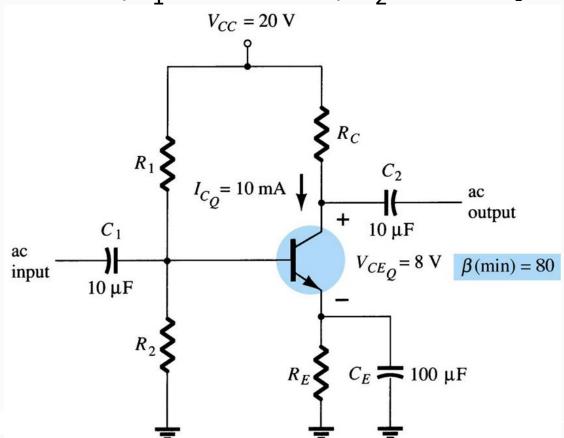

### Exercise : Design

Determine all the resistors  $R_E$ ,  $R_C$ ,  $R_2$  and  $R_1$  values in designing the fixed bias with emitter-stabilized circuit as below. Given  $\beta_{min} = h_{FE(min)} = 80$  and  $V_{BE} = 0.7 \text{ V}$ ,  $V_{CEQ} = 8 \text{ V}$  and  $I_{CQ} = 10 \text{ mA}$ . Assume  $V_E = (1/10)V_{CC}$  and  $\beta R_E = 10R_2$ . [Ans:  $R_F = 197.53\Omega$ , RC =  $1k\Omega$ ,  $R_1 = 10.12 \text{ k}\Omega$ ,  $R_2 = 1.58k\Omega$ ]

innovative • entrepreneurial • global

Exercise

Calculate the value for R<sub>C</sub>, R<sub>B</sub>, V<sub>CE</sub> and  $\beta$  for a fixed bias circuit if V<sub>CC</sub>= 24V, I<sub>B</sub> = 20µA dan I<sub>C</sub> = 3mA. Transistor must properly biased to achieve maximum symmetrical output swing for the voltage and current. Given V<sub>BE</sub> = 0.7V.

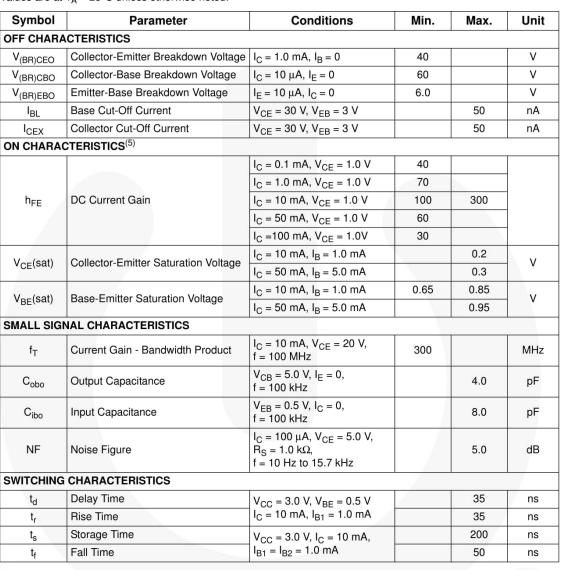

### Example Transistor Specification & Data Sheet

Answer the following questions by referring to the partial transistor data sheet for transistor 2N3904.

- a) What is the maximum collector to emitter voltage?

- b) How much continuous collector current can the 2N3904 handle?

- c) How much power can 2N3904 dissipate if the ambient temperature is 25° C?

- d) What is the minimum and maximum  $\beta$ ?

Data Sheet for BJT

#### Absolute Maximum Ratings<sup>(1), (2)</sup>

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. Values are at  $T_A = 25^{\circ}$ C unless otherwise noted.

| Symbol            | Parameter                                        | Value      | Unit<br>V |  |

|-------------------|--------------------------------------------------|------------|-----------|--|

| V <sub>CEO</sub>  | Collector-Emitter Voltage                        | 40         |           |  |

| V <sub>CBO</sub>  | Collector-Base Voltage                           | 60         | V         |  |

| V <sub>EBO</sub>  | Emitter-Base Voltage                             | 6.0        | V         |  |

| Ι <sub>C</sub>    | Collector Current - Continuous                   | 200        | mA        |  |

| $T_{J_i} T_{STG}$ | Operating and Storage Junction Temperature Range | -55 to 150 | °C        |  |

#### Notes:

1. These ratings are based on a maximum junction temperature of 150°C.

2. These are steady-state limits. Fairchild Semiconductor should be consulted on applications involving pulsed or low-duty cycle operations.

#### **Thermal Characteristics**

Values are at  $T_A = 25^{\circ}C$  unless otherwise noted.

| Symbol                | Parameter                               | Maximum |                         |                        | Unit  |

|-----------------------|-----------------------------------------|---------|-------------------------|------------------------|-------|

|                       |                                         | 2N3904  | MMBT3904 <sup>(3)</sup> | PZT3904 <sup>(4)</sup> |       |

| P <sub>D</sub>        | Total Device Dissipation                | 625     | 350                     | 1,000                  | mW    |

|                       | Derate Above 25°C                       | 5.0     | 2.8                     | 8.0                    | mW/°C |

| $R_{	extsf{	heta}JC}$ | Thermal Resistance, Junction to Case    | 83.3    |                         |                        | °C/W  |

| $R_{	extsf{	heta}JA}$ | Thermal Resistance, Junction to Ambient | 200     | 357                     | 125                    | °C/W  |

#### Notes:

3. Device is mounted on FR-4 PCB 1.6 inch X 1.6 inch X 0.06 inch.

4. Device is mounted on FR-4 PCB 36 mm X 18 mm X 1.5 mm, mounting pad for the collector lead minimum 6 cm<sup>2</sup>.

#### **Electrical Characteristics**

Values are at  $T_A = 25^{\circ}C$  unless otherwise noted.

# 2N3904 / MMBT3904 / PZT3904 NPN General-Purpose Amplifier

Note:

5. Pulse test: pulse width  $\leq$  300 µs, duty cycle  $\leq$  2.0%.